# Capítulo 3

# Linguagem de Montagem

**Autora: Wu Shin-Ting**

Neste capítulo vamos ver como se escreve um programa utilizando uma linguagem de programação próxima aos códigos binários, de forma que um processador conseguiria decodificar imediatamente sem recorrer a um compilador. Esta linguagem é denominada **linguagem de montagem** (assembly).

Embora os códigos em **linguagem de alto nível**, como Fortran, C e Pascal, sejam mais inteligíveis, portáteis e independentes da arquitetura do processador, os **códigos de máquina**, por refletirem diretamente a arquitetura do processador e serem inteligíveis para dispositivos computacionais, permitem os programadores fazerem uma análise mais precisa do desempenho dos códigos e ter um controle maior na sua otimização. Portanto, os códigos de máquina são ainda altamente recomendáveis para aplicações com restrições de desempenho críticas tanto em relação à memória quanto em relação ao tempo de execução.

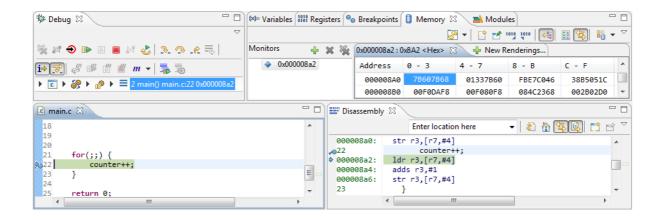

No entanto, os códigos (binários) de máquina, como os mostrados na aba "*Memory*" da Figura 1, são difíceis de entender e um programa desenvolvido com base nestes códigos são susceptíveis a muitos tipos de erros. Uma solução é renderizar os códigos binários em códigos simbólicos mais inteligíveis, como os mostrados na aba "*Disassembly*" da Figura 1. O conjunto destes códigos simbólicos, ou mnemônicos, constitui a linguagem de montagem. Sendo os códigos de máquina uma linguagem da máquina, eles são altamente dependentes da arquitetura do processador. O processador integrado ao nosso microcontrolador é o processador ARM Cortex-M0+, da arquitetura ARM. Ele suporta códigos de máquina de 16 *bits* (*Thumb*) e de 32 *bits* (*Thumb-2*). Nesta disciplina trabalharemos com o repertório de instruções *Thumb* [1]. O montador disponível no IDE CodeWarrior é o montador GNU [2].

Figura 1: Uma instrução em diferentes níveis de abstração

O IDE CodeWarrior provê mecanismos para visualizar, de forma sincronizada, na perspectiva de depuração a correspondência entre os códigos-fonte (linguagem de alto nível) e códigos em *assembly* compilados (códigos mnemônicos próximos da máquina). Na Figura 1 as instruções correspondentes são destacadas com a cor verde.

# 3.1 Linguagem de Máquina e de Montagem (Assembly)

Vamos fazer o seguinte experimento com o programa-exemplo gerado automaticamente pelo IDE CodeWarrior ao criarmos um novo projeto: setarmos na sua perspectiva de depuração um ponto de parada na linha de instrução "counter++; " e executarmos passa-a-passo ("*Step Over*"), no modo "*Instruction Stepping Mode*". Veja na aba "*Disassembly*" que para cada incremento da variável "counter" são executadas 3 instruções de máquina:

```

ldr r3,[r7,#4]

adds r3,#1

str r3,[r7,#4]

```

São chamadas de instruções de máquina, porque cada uma delas corresponde a um código de máquina da arquitetura do processador. Na aba "*Disassembly*" da Figura 1 podemos ver ainda os endereços em que estas instruções são relocadas: 0x000008a2, 0x000008a4 e 0x000008a6. Inserindo o primeiro endereço na aba "*Memory*" temos acesso aos códigos binários armazenados nestes endereços conforme mostra a Figura 1: 0x687B, 0x3301 e 0x607B, respectivamente.

São estes códigos na memória que, de fato, o processador busca, decodifica e executa em cada ciclo de instrução. Se codificarmos o nosso programa em linguagem de alto nível, utilizamos **compiladores** para traduzí-la nestes códigos como vimos no capítulo 2. Quando descrevermos o fluxo de controle do nosso procedimento com uso de mnemônicos, ou *assembly*, usamos **montadores** ou *assemblers* para convertê-los em códigos de máquina. Note que, diferentemente da compilação, a montagem é uma tradução direta de um formato simbólico para um formato binário. Estes dois formatos são, na verdade, duas formas distintas de renderizar um mesmo conjunto de dados. Vamos ver nesta seção a correspondência entre estes dois formatos mais detalhadamente.

#### 3.1.1 Códigos de Operação

Embora seja da arquitetura ARM, o nosso processador suporta somente o repertório de instruções *Thumb* de 16 *bits* e um número bem reduzido de instruções de desvio de 32 *bits* de tecnologia *Thumb-2*. Mesmo suportando somente o modo *Thumb*, o nosso processador segue a convenção de chaveamento entre o repertório de instruções ARM e o de *Thumb* através do *bit* 0 dos endereços. Este *bit* não é usado no endereçamento. Quando ele é 1, o modo de instrução é chaveado para *Thumb*; do contrário, para o modo ARM de 32 *bits*. Por este motivo, o PC é sempre inicializado

com um endereço ímpar.

As instruções *Thumb* de 32 *bits* são reservadas para operações bem específicas, como chaveamento entre os modos ARM e *Thumb* e o controle de transferência de dados dos registradores especiais, como mostra a Figura 2.

| ľ | 15 | 14 | 13 | 12 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|---|----|----|----|-------|----|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|--------|

| Γ | 1  | 1  | 1  | op1   |    |   |   |   |   |   |   |   |   |   |   | ор |    |    |    |    |    |   |   |   |   |   |   |   |   |   | $\neg$ |

For 32-bit Thumb encoding, op 1! = 0b00. If op 1 == 0b00, a 16-bit instruction is encoded, see 16-bit Thumb instruction encoding on page A5-84.

Table A5-9 shows the allocation of ARMv6-M Thumb encodings in this space.

#### Table A5-9 32-bit Thumb encoding

| op1 | ор | Instruction class                    |

|-----|----|--------------------------------------|

| x1  | Х  | UNDEFINED                            |

| 10  | 1  | See Branch and miscellaneous control |

| 10  | 0  | UNDEFINED                            |

Figura 2: Códigos de operação das instruções *Thumb* de 32 *bits*.

O repertório de instruções *Thumb* de 16 *bits* inclui os códigos de processamento de dados numéricos inteiros, os códigos de desvio, os códigos de acesso aos registradores de estado APSR (*Application Program Status Register*), os códigos de acesso à "memória" endereçável através do espaço de endereços de 32 *bits*, os códigos de acesso múltiplo à "memória", e os códigos de geração forçada de exceções. Figura 3 apresenta um sumário dos códigos de operação do repertório *Thumb* de 16 *bits*. No capítulo A.6 em [1] são detalhados a sintaxe de cada instrução *Thumb* e o respectivo código binário. Uma referência rápida do conjunto completo de instruções é encontrada em [3].

| 15 14 13 12 11 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|---|---|---|---|---|---|---|---|---|---|

| opcode            |   |   |   |   |   |   |   |   |   |   |

Table A5-1 shows the allocation of 16-bit instruction encodings.

Table A5-1 16-bit Thumb instruction encoding

| opcode | Instruction or instruction class                                         |

|--------|--------------------------------------------------------------------------|

| 00xxxx | Shift (immediate), add, subtract, move, and compare on page A5-85        |

| 010000 | Data processing on page A5-86                                            |

| 010001 | Special data instructions and branch and exchange on page A5-87          |

| 01001x | Load from Literal Pool, see LDR (literal) on page A6-141                 |

| 0101xx | Load/store single data item on page A5-88                                |

| 011xxx |                                                                          |

| 100xxx |                                                                          |

| 10100x | Generate PC-relative address, see ADR on page A6-115                     |

| 10101x | Generate SP-relative address, see ADD (SP plus immediate) on page A6-111 |

| 1011xx | Miscellaneous 16-bit instructions on page A5-89                          |

| 11000x | Store multiple registers, see STM, STMIA, STMEA on page A6-175           |

| 11001x | Load multiple registers, see LDM, LDMIA, LDMFD on page A6-137            |

| 1101xx | Conditional branch, and Supervisor Call on page A5-90                    |

| 11100x | Unconditional Branch, see B on page A6-119                               |

Figura 3: Códigos de operação do repertório Thumb (Fonte: A5.2 em [1]).

## 3.1.2 Formato de Instruções

As instruções *Thumb* são constituídas de dois campos: o campo de código de operação e o campo de argumentos. A quantidade de argumentos no segundo campo varia entre 0 a 3 operandos. Por exemplo,

Código de Operação Argumentos adds r3,#1

Opcionalmente, podemos adicionar ainda dois outros campos: o campo de rótulo e o campo de comentários. Todos os rótulos devem ser seguidos de ":", enquanto o(s) caracteres que deve(m) preceder são dependentes do processador. Usualmente é ";". Porém, para arquitetura i386 e x86\_64, ele é "#" e para ARM é "@". No ambiente IDE CodeWarrior, podemos ainda utilizar a sintaxe de comentários de C /\* \*/. Por exemplo,

| Rótulo | Código de Operação | Operandos | Comentários          |

|--------|--------------------|-----------|----------------------|

| INC:   | adds               | r3,#1     | @ $R3 := [R3] + 1$   |

| INC:   | adds               | r3,#1     | /* R3 := [R3] + 1 */ |

Vale frisar que cada linha do arquivo de um código de montagem só pode conter até um conjunto destes campos, que não necessariamente precisam estar preenchidos.

#### 3.1.3 Modos de Endereçamento

Quando se trata de instruções que manipulam os dados, somente o modo de endereçamento por registrador e o modo de endereçamento imediato são suportados. Observe na coluna "Assembler" da Figura 4 que os argumentos das instruções são registradores (Rd, Rm) ou um valor numérico <imm> precedido por #. Com exceção de algumas instruções que operam sobre o ponteiro da pilha (*stack pointer*), SP, somente os 8 registradores de trabalho R0-R7 podem ser utilizados nas instruções *Thumb*. Os símbolos R e # que aparecem numa instrução em linguagem de montagem (*assembly*) dizem para o montador que tanto o número do registrador quanto o valor <imm> devem ser codificados no próprio código de operação.

| Operation    | ·                            | §  | Assembler                      | ι | Jpdat | es       | Action                         | Notes                                                               |

|--------------|------------------------------|----|--------------------------------|---|-------|----------|--------------------------------|---------------------------------------------------------------------|

| Move         | Immediate                    |    | MOVS Rd, # <imm></imm>         | N | Z     |          | Rd := imm                      | imm range 0-255.                                                    |

|              | Lo to Lo                     |    | MOVS Rd, Rm                    | N | Z     |          | Rd := Rm                       | Synonym of LSLS Rd, Rm, #0                                          |

|              | Hi to Lo, Lo to Hi, Hi to Hi |    | MOV Rd, Rm                     |   |       |          | Rd := Rm                       | Not Lo to Lo.                                                       |

|              | Any to Any                   | 6  | MOV Rd, Rm                     |   |       |          | Rd := Rm                       | Any register to any register.                                       |

| Add          | Immediate 3                  |    | ADDS Rd, Rn, # <imm></imm>     | N | Z (   | . v      | Rd := Rn + imm                 | imm range 0-7.                                                      |

|              | All registers Lo             |    | ADDS Rd, Rn, Rm                | N | Z (   | . v      | Rd := Rn + Rm                  |                                                                     |

|              | Hi to Lo, Lo to Hi, Hi to Hi |    | ADD Rd, Rd, Rm                 |   |       |          | Rd := Rd + Rm                  | Not Lo to Lo.                                                       |

|              | Any to Any                   | T2 | ADD Rd, Rd, Rm                 |   |       |          | Rd := Rd + Rm                  | Any register to any register.                                       |

|              | Immediate 8                  |    | ADDS Rd, Rd, # <imm></imm>     | N | Z (   | . v      | Rd := Rd + imm                 | imm range 0-255.                                                    |

|              | With carry                   |    | ADCS Rd, Rd, Rm                | N | Z (   | . v      | Rd := Rd + Rm + C-bit          |                                                                     |

|              | Value to SP                  |    | ADD SP, SP, # <imm></imm>      |   |       |          | SP := SP + imm                 | imm range 0-508 (word-aligned).                                     |

|              | Form address from SP         |    | ADD Rd, SP, # <imm></imm>      |   |       |          | Rd := SP + imm                 | imm range 0-1020 (word-aligned).                                    |

|              | Form address from PC         |    | ADR Rd, <label></label>        |   |       |          | Rd := label                    | label range PC to PC+1020 (word-aligned).                           |

| Subtract     | Lo and Lo                    |    | SUBS Rd, Rn, Rm                | N | Z (   | . v      | Rd := Rn - Rm                  |                                                                     |

|              | Immediate 3                  |    | SUBS Rd, Rn, # <imm></imm>     | N | Z     | . v      | Rd := Rn - imm                 | imm range 0-7.                                                      |

|              | Immediate 8                  |    | SUBS Rd, Rd, # <imm></imm>     | N | Z (   | V        | Rd := Rd - imm                 | imm range 0-255.                                                    |

|              | With carry                   |    | SBCS Rd, Rd, Rm                | N | Z (   | . V      | Rd := Rd - Rm - NOT C-bit      |                                                                     |

|              | Value from SP                |    | SUB SP, SP, # <imm></imm>      |   |       |          | SP := SP - imm                 | imm range 0-508 (word-aligned).                                     |

|              | Negate                       |    | RSBS Rd, Rn, #0                | N | Z (   | 2 V      | Rd := -Rn                      | Synonym: NEG Rd, Rn                                                 |

| Multiply     | Multiply                     |    | MULS Rd, Rd, Rm                | N | Z     | * *      | Rd := Rm * Rd                  | * C and V flags unpredictable in §4T,<br>unchanged in §5T and above |

| Compare      |                              |    | CMP Rn, Rm                     | N | Z (   | 2 V      | update CPSR flags on Rn - Rm   | Can be Lo to Lo, Lo to Hi, Hi to Lo, or Hi to Hi.                   |

|              | Negative                     |    | CMN Rn, Rm                     | N | Z (   | . V      | update CPSR flags on Rn + Rm   |                                                                     |

|              | Immediate                    |    | CMP Rn, # <imm></imm>          | N | Z (   | . V      | update CPSR flags on Rn - imm  | imm range 0-255.                                                    |

| Logical      | AND                          |    | ANDS Rd, Rd, Rm                | N | Z     |          | Rd := Rd AND Rm                |                                                                     |

|              | Exclusive OR                 |    | EORS Rd, Rd, Rm                | N | Z     |          | Rd := Rd EOR Rm                |                                                                     |

|              | OR                           |    | ORRS Rd, Rd, Rm                | N | Z     |          | Rd := Rd OR Rm                 |                                                                     |

|              | Bit clear                    |    | BICS Rd, Rd, Rm                | N | Z     |          | Rd := Rd AND NOT Rm            |                                                                     |

|              | Move NOT                     |    | MVNS Rd, Rd, Rm                | N | Z     |          | Rd := NOT Rm                   |                                                                     |

|              | Test bits                    |    | TST Rn, Rm                     | N | Z     |          | update CPSR flags on Rn AND Rm |                                                                     |

| Shift/rotate | Logical shift left           |    | LSLS Rd, Rm, # <shift></shift> | N | Z     | ]*       | Rd := Rm << shift              | Allowed shifts 0-31. * C flag unaffected if shift is 0.             |

|              |                              |    | LSLS Rd, Rd, Rs                | N | Z C   | <b>*</b> | Rd := Rd << Rs[7:0]            | * C flag unaffected if Rs[7:0] is 0.                                |

|              | Logical shift right          |    | LSRS Rd, Rm, # <shift></shift> | N | Z     | 2        | Rd := Rm >> shift              | Allowed shifts 1-32.                                                |

|              |                              |    | LSRS Rd, Rd, Rs                | N | Z C   | *        | Rd := Rd >> Rs[7:0]            | * C flag unaffected if Rs[7:0] is 0.                                |

|              | Arithmetic shift right       |    | ASRS Rd, Rm, # <shift></shift> | N | Z     | 2        | Rd := Rm ASR shift             | Allowed shifts 1-32.                                                |

|              |                              |    | ASRS Rd, Rd, Rs                | N | Z     | *        | Rd := Rd ASR Rs[7:0]           | * C flag unaffected if Rs[7:0] is 0.                                |

|              | Rotate right                 |    | RORS Rd, Rd, Rs                | N | Z C   | *        | Rd := Rd ROR Rs[7:0]           | * C flag unaffected if Rs[7:0] is 0.                                |

Figura 4: Instruções de processamento de dados (Fonte: [3]).

Por exemplo, o código de máquina do código de operação ADDS é o apresentado na Figura 5. O montador traduz a instrução "adds r3,#1" para o código binário 0b001 10 011 00000001, um vez que o valor "1" é codificado no campo <imm8> (bits 7-0) e o número do registrador r3 é codificado no campo <Rdn> (bits 10-8) do código. Em hexadecimal, o código de máquina da instrução é

0x3301 como vimos na aba "Memory".

### **Encoding T2** All versions of the Thumb instruction set.

ADDS <Rdn>,#<imm8>

| 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|----|----|----|----|----|----|-----|---|---|---|---|----|----|---|---|---|

| 0  | 0  | 1  | 1  | 0  | F  | ₹dr | 1 |   |   |   | im | m8 |   |   |   |

```

d = UInt(Rdn); n = UInt(Rdn); setflags = !InITBlock(); imm32 = ZeroExtend(imm8, 32);

```

Figura 5: Código de máquina da instrução ADDS (Fonte: Seção A 6.7.2 em [1]).

Caso seja necessário processar os dados que não estejam carregados nos registradores, deve-se usar instruções de acesso à "memória" para fazer transferência de dados entre a "memória" e os registradores, como mostra a sequência de 3 códigos de operação apresentada na introdução da Seção 3.1: ldr (carrega no registrador), adds (soma) e str (armazena na memória). Para acessos à "memória", temos mais opções em modos de endereçamento como mostra a coluna "Assembler" da tabela da Figura 6. São suportados o modo de deslocamento imediato e via registrador a partir do endereço no registrador-base Rn (Seção A4.6.2 em [1]).

| Operatio | n                            | §  | Assembler                          | Action                                                 | Notes                                          |

|----------|------------------------------|----|------------------------------------|--------------------------------------------------------|------------------------------------------------|

| Load     | with immediate offset, word  |    | LDR Rd, [Rn, # <imm>]</imm>        | Rd := [Rn + imm]                                       | imm range 0-124, multiple of 4.                |

|          | halfword                     |    | LDRH Rd, [Rn, # <imm>]</imm>       | Rd := ZeroExtend([Rn + imm][15:0])                     | Clears bits 31:16. imm range 0-62, even.       |

|          | byte                         |    | LDRB Rd, [Rn, # <imm>]</imm>       | Rd := ZeroExtend([Rn + imm][7:0])                      | Clears bits 31:8. imm range 0-31.              |

|          | with register offset, word   |    | LDR Rd, [Rn, Rm]                   | Rd := [Rn + Rm]                                        |                                                |

|          | halfword                     |    | LDRH Rd, [Rn, Rm]                  | Rd := ZeroExtend([Rn + Rm][15:0])                      | Clears bits 31:16                              |

|          | signed halfword              |    | LDRSH Rd, [Rn, Rm]                 | Rd := SignExtend([Rn + Rm][15:0])                      | Sets bits 31:16 to bit 15                      |

|          | byte                         |    | LDRB Rd, [Rn, Rm]                  | Rd := ZeroExtend([Rn + Rm][7:0])                       | Clears bits 31:8                               |

|          | signed byte                  |    | LDRSB Rd, [Rn, Rm]                 | Rd := SignExtend([Rn + Rm][7:0])                       | Sets bits 31:8 to bit 7                        |

|          | PC-relative                  |    | LDR Rd, <label></label>            | Rd := [label]                                          | label range PC to PC+1020 (word-aligned).      |

|          | SP-relative                  |    | LDR Rd, [SP, # <imm>]</imm>        | Rd := [SP + imm]                                       | imm range 0-1020, multiple of 4.               |

|          | Multiple, not including base |    | LDM Rn!, <loreglist></loreglist>   | Loads list of registers (not including Rn)             | Always updates base register, Increment After. |

|          | Multiple, including base     |    | LDM Rn, <loreglist></loreglist>    | Loads list of registers (including Rn)                 | Never updates base register, Increment After.  |

| Store    | with immediate offset, word  |    | STR Rd, [Rn, # <imm>]</imm>        | [Rn + imm] := Rd                                       | imm range 0-124, multiple of 4.                |

|          | halfword                     |    | STRH Rd, [Rn, # <imm>]</imm>       | [Rn + imm][15:0] := Rd[15:0]                           | Ignores Rd[31:16]. imm range 0-62, even.       |

|          | byte                         |    | STRB Rd, [Rn, # <imm>]</imm>       | [Rn + imm][7:0] := Rd[7:0]                             | Ignores Rd[31:8]. imm range 0-31.              |

|          | with register offset, word   |    | STR Rd, [Rn, Rm]                   | [Rn + Rm] := Rd                                        |                                                |

|          | halfword                     |    | STRH Rd, [Rn, Rm]                  | [Rn + Rm][15:0] := Rd[15:0]                            | Ignores Rd[31:16]                              |

|          | byte                         |    | STRB Rd, [Rn, Rm]                  | [Rn + Rm][7:0] := Rd[7:0]                              | Ignores Rd[31:8]                               |

|          | SP-relative, word            |    | STR Rd, [SP, # <imm>]</imm>        | [SP + imm] := Rd                                       | imm range 0-1020, multiple of 4.               |

|          | Multiple                     |    | STM Rn!, <loreglist></loreglist>   | Stores list of registers                               | Always updates base register, Increment After. |

| Push     | Push                         |    | PUSH <loreglist></loreglist>       | Push registers onto full descending stack              |                                                |

|          | Push with link               |    | PUSH <loreglist+lr></loreglist+lr> | Push LR and registers onto full descending stack       |                                                |

| Pop      | Pop                          |    | POP <loreglist></loreglist>        | Pop registers from full descending stack               |                                                |

|          | Pop and return               | 4T | POP <loreglist+pc></loreglist+pc>  | Pop registers, branch to address loaded to PC          |                                                |

|          | Pop and return with exchange | 5T | POP <loreglist+pc></loreglist+pc>  | Pop, branch, and change to ARM state if address[0] = 0 |                                                |

Figura 6: Instruções de transferência de dados entre registradores e memória (Fonte: [3]).

Por exemplo, o modo de endereçamento da instrução "ldr r3,[r7,#4]" é o modo de deslocamento imediato (ou modo de endereçamento indireto), pois o endereço acessado é a soma do conteúdo do registrador-base R7 e o valor 4. E o conteúdo deste endereço é carregado no registrador R3. O montador entende que é o conteúdo por causa dos colchetes []. O código de máquina da instrução LDR é mostrado na Figura 7. Vamos ver como o montador traduz a instrução. O valor 4 é colocado no campo <imm5> (bits 10-6), o número do registrador-destino R3 é armazenado no campo <Rt> (bits 2-0) e o do registrador-base no campo <Rn> (bits 5-3). Portanto, o código de máquina correspondente à instrução é 0b011 0 1 00100 111 011. Em hexadecimal, é 0x687B como vimos na

aba "*Memory*". O argumento [Rn,Rm] nas instruções da Figura 6 representa o modo de deslocamento via registrador. O valor a ser armazenado no registrador destino <Rt> é o conteúdo do endereço definido pela soma do conteúdo dos registradores Rn e Rm.

Vale ressaltar aqui que a versão LDR que usa o contador de programa, PC, como registrador-base é muito utilizada pelo comiplador do nosso IDE CodeWarrior. A maioria dos dados residentes na memória tem os seus endereços especificados como um valor deslocado em relação ao PC nas instruções de montagem após a compilação. Conforme mostra a Seção A 6.7.26 em [1], este valor de deslocamento é codificado na própria instrução, em 5 *bits* ou em 8 *bits*. Porém, a faixa de valores de deslocamento (*offset*) é 7 e 10 *bits*, respectivamente. Pois, o processador assume que os endereços sejam sempre múltiplos de 4 e automaticamente complementa o valor binário codificado na instrução com dois dígitons binários menos significativos "00". Figura 7 ilustra a instrução LDR tendo PC como registrador-base. O valor de deslocamento codificado no campo "imm5" deve ser complementado com "00" antes de somá-lo com o endereço no PC.

## **Encoding T1** All versions of the Thumb instruction set.

LDR <Rt>, [<Rn>{,#<imm5>}]

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7 | 6 | 5 | 4  | 3 | 2 | 1  | 0 |

|----|----|----|----|----|----|----|----|---|---|---|----|---|---|----|---|

| 0  | 1  | 1  | 0  | 1  |    | ir | nm | 5 |   |   | Rn |   |   | Rt |   |

```

t = UInt(Rt); n = UInt(Rn); imm32 = ZeroExtend(imm5:'00', 32);

index = TRUE; add = TRUE; wback = FALSE;

```

Figura 7: Código de máquina da instrução LDR (Fonte: Seção A 6.7.26 em [1]).

Quando se deseja transferir um bloco de dados da pilha entre um conjunto de registradores, pode-se utilizar códigos de operação **pop** e **push**. O conjunto de registradores de interesse, separados pela vírgula, deve ser fechado entre as chaves. Só um lembrete: como o endereço do topo da pilha está armazenado no registrador SP (*stack pointer*), são duas instruções de transferência especiais que tem como registrador-base o registrador SP.

Há uma instrução em *assembly* que não faz nada absolutamente e força a execução de um ciclo de instrução que corresponde a um ciclo de relógio. Ela é a instrução **nop**. Essa instrução pode ser encontrada em várias situações em que se precisa "sincronizar" o tempo de execução de um bloco de códigos com outros blocos ou com um intervalo de tempo pré-estabelecido. No entanto, de acordo com a Seção A6.7.47 de [1], que os efeitos da instrução *thumb* NOP são imprevisíveis; portanto, deve-se evitar o seu uso no controle de atrasos.

Encoding T1 ARMv6-M, ARMv7-M

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

// No additional decoding required

Figura 8: Código de máquina da instrução NOP (Fonte: Seção A 6.7.47 em [1]).

#### 3.1.4 Desvios

O repertório de instruções *Thumb* inclui as instruções de desvio, conforme mostra a Figura 9.

|         | 1 -                           |    | t contract the contract to the |                                                                                                                                                                 | t and the second |

|---------|-------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| If-Then | If-Then                       | T2 | IT(pattern) (cond)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Makes up to four following instructions conditional, according to pattern. pattern is a string of up to three letters. Each letter can be T (Then) or E (Else). | The first instruction after IT has condition cond. The following instructions have condition cond if the corresponding letter is T, or the inverse of cond if the corresponding letter is E. See Table <b>Condition Field</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Branch  | Conditional branch            |    | B(cond) <label></label>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | If {cond} then PC := label                                                                                                                                      | label must be within – 252 to + 258 bytes of current instruction.<br>See Table <b>Condition Field</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | Compare, branch if (non) zero | T2 | CB{N}Z Rn, <label></label>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | If Rn {==   !=} 0 then PC := label                                                                                                                              | label must be within +4 to +130 bytes of current instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | Unconditional branch          |    | B <label></label>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PC := label                                                                                                                                                     | label must be within ±2KB of current instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | Long branch with link         |    | BL <label></label>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LR := address of next instruction, PC := label                                                                                                                  | This is a 32-bit instruction. label must be within ±4MB of current instruction (T2: ±16MB).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | Branch and exchange           |    | BX Rm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PC := Rm AND 0xFFFFFFE                                                                                                                                          | Change to ARM state if Rm[0] = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | Branch with link and exchange | 5T | BLX <label></label>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LR := address of next instruction, PC := label<br>Change to ARM                                                                                                 | This is a 32-bit instruction. label must be within ±4MB of current instruction (T2: ±16MB).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | Branch with link and exchange | 5T | BLX Rm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LR := address of next instruction,<br>PC := Rm AND 0xFFFFFFE                                                                                                    | Change to ARM state if Rm[0] = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |                               |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Figura 9: Instruções de desvio (Fonte: [3]).

Observe que algumas instruções correspondem aos desvios condicionados aos valores dos *bits* de condição N(*egative*), Z(*ero*), C(*arry*) e (*o*)V(*erflow*) do registrador de estado APSR. Estes *bits* são, usualmente, atualizados conforme o resultado de uma instrução que manipula os dados. No entanto, na arquitetura ARM algumas instruções não modificam tais *bits* automaticamente, como ADD (Seção A6.7.3 em [1])) e MOV (Seção A6.7.40 em [1]). Para cada uma destas instruções existe uma versão correspondente que atualiza os *bits* de condição. Ela é diferenciada pelo sufixo S, como ADDS e MOVS. Os mnemônicos utilizados para os desvios condicionados mais utilizados são EQ (igual), NE (diferente), CS (*Carry* em 1), CC (*Carry* em 0), MI (negativo), PL (>=), VS (*Overflow* em 1), VC (*Overflow* em 0), GE (>=), LT (<), GT (>), LE (<=) precedidos de B.

#### 3.1.5 Ciclos de Instrução

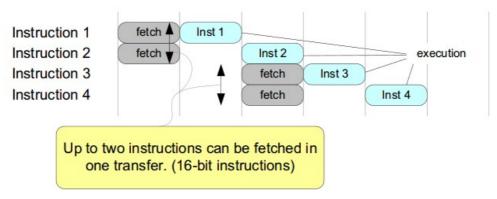

A arquitetura ARM foi concebida de forma que a maioria das instruções de processamento dos dados leva apenas um ciclo de relógio para ser executada como mostra a Figura 10. Ou seja, o ciclo de execução dessas instruções corresponde a um ciclo de relógio. O processador Cortex-M0+, integrado no nosso microcontrolador, suporta as instruções de multiplicação em 32-*bit*s. Elas

apresentam tempos de execução diferenciados como consta na Figura 10. Informações adicionais podem ser consultadas na Tabela 3.1 em [5].

Table 3-1 Cortex-M0+ instruction summary

| Operation | Description          | Assembler                  | Cycles |

|-----------|----------------------|----------------------------|--------|

| Move      | 8-bit immediate      | MOVS Rd, # <imm></imm>     | 1      |

|           | Lo to Lo             | MOVS Rd, Rm                | 1      |

|           | Any to Any           | MOV Rd, Rm                 | 1      |

|           | Any to PC            | MOV PC, Rm                 | 2      |

| Add       | 3-bit immediate      | ADDS Rd, Rn, # <imm></imm> | 1      |

|           | All registers Lo     | ADDS Rd, Rn, Rm            | 1      |

|           | Any to Any           | ADD Rd, Rd, Rm             | 1      |

|           | Any to PC            | ADD PC, PC, Rm             | 2      |

|           | 8-bit immediate      | ADDS Rd, Rd, # <imm></imm> | 1      |

|           | With carry           | ADCS Rd, Rd, Rm            | 1      |

|           | Immediate to SP      | ADD SP, SP, # <imm></imm>  | 1      |

|           | Form address from SP | ADD Rd, SP, # <imm></imm>  | 1      |

|           | Form address from PC | ADR Rd, <1abe1>            | 1      |

| Subtract | Negate    | RSBS Rd, Rn, #0       | 1        |

|----------|-----------|-----------------------|----------|

| Multiply | Multiply  | MULS Rd, Rm, Rd       | 1 or 32a |

| Compare  | Compare   | CMP Rn, Rm            | 1        |

|          | Negative  | CMN Rn, Rm            | 1        |

|          | Immediate | CMP Rn, # <imm></imm> | 1        |

| Rotate | Rotate right by register         | RORS Rd, Rd, Rs                     | 1                   |

|--------|----------------------------------|-------------------------------------|---------------------|

| Load   | Word, immediate offset           | LDR Rd, [Rn, # <imm>]</imm>         | 2 or 1 <sup>b</sup> |

|        | Halfword, immediate offset       | LDRH Rd, [Rn, # <imm>]</imm>        | 2 or 1 <sup>b</sup> |

|        | Byte, immediate offset           | LDRB Rd, [Rn, # <imm>]</imm>        | 2 or 1 <sup>b</sup> |

|        | Word, register offset            | LDR Rd, [Rn, Rm]                    | 2 or 1 <sup>b</sup> |

|        | Halfword, register offset        | LDRH Rd, [Rn, Rm]                   | 2 or 1 <sup>b</sup> |

|        | Signed halfword, register offset | LDRSH Rd, [Rn, Rm]                  | 2 or 1 <sup>b</sup> |

|        | Byte, register offset            | LDRB Rd, [Rn, Rm]                   | 2 or 1 <sup>b</sup> |

| Load   | Signed byte, register offset     | LDRSB Rd, [Rn, Rm]                  | 2 or 1 <sup>b</sup> |

|        | PC-relative                      | LDR Rd, <1abe1>                     | 2 or 1 <sup>b</sup> |

|        | SP-relative                      | LDR Rd, [SP, # <imm>]</imm>         | 2 or 1 <sup>b</sup> |

|        | Multiple, excluding base         | LDM Rn!, { <loreglist>}</loreglist> | 1+N°                |

|        | Multiple, including base         | LDM Rn, { <loreglist>}</loreglist>  | 1+Nc                |

| Store  | Word, immediate offset     | STR Rd, [Rn, # <imm>]</imm>         | 2 or 1 <sup>b</sup> |

|--------|----------------------------|-------------------------------------|---------------------|

|        | Halfword, immediate offset | STRH Rd, [Rn, # <imm>]</imm>        | 2 or 1 <sup>b</sup> |

|        | Byte, immediate offset     | STRB Rd, [Rn, # <imm>]</imm>        | 2 or 1 <sup>b</sup> |

|        | Word, register offset      | STR Rd, [Rn, Rm]                    | 2 or 1 <sup>b</sup> |

|        | Halfword, register offset  | STRH Rd, [Rn, Rm]                   | 2 or 1 <sup>b</sup> |

|        | Byte, register offset      | STRB Rd, [Rn, Rm]                   | 2 or 1 <sup>b</sup> |

|        | SP-relative                | STR Rd, [SP, # <imm>]</imm>         | 2 or 1 <sup>b</sup> |

|        | Multiple                   | STM Rn!, { <loreglist>}</loreglist> | 1+N°                |

| Push   | Push                       | PUSH { <loreglist>}</loreglist>     | 1+N°                |

|        | Push with link register    | PUSH { <loreglist>, LR}</loreglist> | 1+N <sup>d</sup>    |

| Pop    | Pop                        | POP { <loreglist>}</loreglist>      | 1+N°                |

|        | Pop and return             | POP { <loreglist>, PC}</loreglist>  | 3+Nd                |

| Branch | Conditional                | B <cc> <label></label></cc>         | 1 or 2e             |

|        | Unconditional              | B <label></label>                   | 2                   |

Figura 10: Tempos de execução de instruções de processamento de dados (Fonte: Seção 3.3 em [5]).