## Kinetis L Peripheral Module Quick Reference

A Compilation of Demonstration Software for Kinetis L Series Modules

This collection of code examples, useful tips, and quick reference material has been created to help you speed the development of your applications. Most chapters in this document contain examples that can be modified to work with Kinetis MCU Family members. When you're developing your application, consult your device data sheet and reference manual for part-specific information, such as which features are supported on your device.

Sample code can be found at KL25\_SC.exe, available from:

www.freescale.com/files/32bit/software/KL25\_SC.exe

Information about the ARM core can be found in the help center at ARM.com

The most up-to-date revisions of our documents are on the Web. Your printed copy may be an earlier revision. To verify that you have the latest information available, refer to freescale.com

## **Revision History**

| Date    | Revision<br>Level | Description     | Page<br>Number(s) |

|---------|-------------------|-----------------|-------------------|

| 09/2012 | 0                 | Initial release | N/A               |

#### **Contents**

| Section number |        | number     | Title                                                       | Page |  |

|----------------|--------|------------|-------------------------------------------------------------|------|--|

|                |        |            | Chapter 1<br>General System Setup (Software Considerations) |      |  |

| 1.1            | Softwa | are consid | erations                                                    | 11   |  |

|                | 1.1.1  | Overvie    | W                                                           | 11   |  |

|                | 1.1.2  | Code ex    | ecution                                                     | 11   |  |

|                | 1.1.3  | Reset an   | d booting                                                   | 11   |  |

|                |        | 1.1.3.1    | Device state during reset                                   | 12   |  |

|                |        | 1.1.3.2    | Device state after reset.                                   | 12   |  |

|                | 1.1.4  | Typical    | system initialization                                       | 12   |  |

|                |        | 1.1.4.1    | Lowest level assembly routines                              | 12   |  |

|                |        |            | 1.1.4.1.1 Initialize general purpose registers              | 12   |  |

|                |        |            | 1.1.4.1.1.1 Unmask interrupts at ARM core                   | 13   |  |

|                |        |            | 1.1.4.1.1.2 Branch to start of C initialization code        | 13   |  |

|                |        | 1.1.4.2    | Startup routines                                            | 13   |  |

|                |        |            | 1.1.4.2.1 Disable watchdog                                  | 13   |  |

|                |        |            | 1.1.4.2.2 Initialize RAM                                    | 13   |  |

|                |        |            | 1.1.4.2.3 Enable port clocks                                | 13   |  |

|                |        |            | 1.1.4.2.4 Ramp system clock to selected frequency           | 13   |  |

|                |        |            | 1.1.4.2.5 Enable pin interrupt                              | 14   |  |

|                |        |            | 1.1.4.2.6 Enable UART for terminal communication.           | 14   |  |

|                |        |            | 1.1.4.2.7 Jump to start of main function for application    | 14   |  |

|                |        |            | Chapter 2 General System Setup (Hardware Considerations)    |      |  |

| 2.1            | Hardw  | are consid | derations                                                   | 15   |  |

|                | 2.1.1  | Overvie    | W                                                           | 15   |  |

|                | 2.1.2  | Floorpla   | n                                                           | 15   |  |

|                |        | 2.1.2.1    | Connectors                                                  | 16   |  |

| Se  | ction i | numbei   | r Title                                             | Page |

|-----|---------|----------|-----------------------------------------------------|------|

|     | 2.1.3   | PCB rou  | uting considerations                                | 16   |

|     |         | 2.1.3.1  | Power supply routing.                               | 16   |

|     |         | 2.1.3.2  | Power supply decoupling and filtering.              | 17   |

|     |         | 2.1.3.3  | Oscillators                                         | 18   |

|     |         |          | 2.1.3.3.1 MCG oscillator                            | 18   |

|     |         | 2.1.3.4  | General filtering.                                  | 23   |

|     |         |          | 2.1.3.4.1 RESET_b and NMI_b                         | 23   |

|     |         |          | 2.1.3.4.2 General purpose I/O                       | 23   |

|     |         |          | 2.1.3.4.3 Analog inputs                             | 23   |

|     | 2.1.4   | PCB lay  | ver stack-up                                        | 24   |

|     | 2.1.5   | Other m  | odule hardware considerations                       | 26   |

|     |         | 2.1.5.1  | Debug interface                                     | 26   |

| 3.1 | NVIC    |          | Chapter 3 Nested Vector Interrupt Controller (NVIC) | 29   |

|     | 3.1.1   | Overvie  | w                                                   | 29   |

|     |         | 3.1.1.1  | Introduction                                        | 29   |

|     |         | 3.1.1.2  | Features                                            | 29   |

|     | 3.1.2   | Configu  | ration examples                                     | 30   |

|     |         | 3.1.2.1  | Configuring the NVIC                                | 30   |

|     |         |          | 3.1.2.1.1 Code example and explanation              | 30   |

|     |         | 3.1.2.2  | Relocating the vector table                         | 32   |

|     |         |          | 3.1.2.2.1 Code example and explanation              | 32   |

|     |         |          | Chapter 4 Clocking System                           |      |

| 1.1 | Clock   | ing      |                                                     | 33   |

|     | 4.1.1   | Overvie  | w                                                   | 33   |

|     | 4.1.2   | Features | 5                                                   | 33   |

| Section number |         | number     | Title                                                 | Page |  |

|----------------|---------|------------|-------------------------------------------------------|------|--|

|                | 4.1.3   | Configu    | ration examples                                       | 35   |  |

|                |         | 4.1.3.1    | Configuring the RTC clock source                      | 37   |  |

|                | 4.1.4   | Addition   | nal clock options                                     | 38   |  |

|                |         | 4.1.4.1    | Compute operation                                     | 39   |  |

|                |         | 4.1.4.2    | Partial stop                                          | 39   |  |

|                | 4.1.5   | Clocking   | g system device hardware implementation               | 40   |  |

|                | 4.1.6   | Layout g   | guidelines for general routing and placement          | 40   |  |

|                | 4.1.7   | Referen    | ces                                                   | 41   |  |

|                |         |            | Chapter 5 Power Management Control (PMC/SMC/LLWU/RCM) |      |  |

| 5.1            | Introdu | uction     |                                                       | 43   |  |

| 5.2            | Using   | the power  | r management controller                               | 43   |  |

|                | 5.2.1   | Overvie    | w                                                     | 43   |  |

|                | 5.2.2   | Using th   | ne low voltage detection system                       | 43   |  |

|                |         | 5.2.2.1    | POR and LVD features.                                 | 43   |  |

|                |         | 5.2.2.2    | Configuration examples.                               | 44   |  |

|                |         | 5.2.2.3    | Interrupt code example and explanation.               | 45   |  |

|                |         | 5.2.2.4    | Hardware implementation.                              | 46   |  |

| 5.3            | Using   | the systen | n mode controller                                     | 48   |  |

|                | 5.3.1   | Overvie    | W                                                     | 48   |  |

|                |         | 5.3.1.1    | Introduction                                          | 48   |  |

|                |         | 5.3.1.2    | Entering and exiting power modes.                     | 49   |  |

|                | 5.3.2   | Configu    | ration examples                                       | 50   |  |

|                |         | 5.3.2.1    | SMC code example and explanation                      | 50   |  |

|                |         | 5.3.2.2    | Entering Low Leakage Stop (LLS) mode                  | 51   |  |

|                |         |            | 5.3.2.2.1 Mode Entry Sequence Serialization           | 51   |  |

|                |         | 5.3.2.3    | Entering wait mode                                    | 52   |  |

|                |         | 5.3.2.4    | Exiting low-power modes                               | 52   |  |

| Section number |                |              | r Title                                          | Page |

|----------------|----------------|--------------|--------------------------------------------------|------|

| 5.4            | Using          | the low le   | eakage wakeup unit                               | 53   |

|                | 5.4.1          | Overvie      | w                                                | 53   |

|                |                | 5.4.1.1      | Mode transitions                                 | 53   |

|                |                | 5.4.1.2      | Wake-up sources                                  | 53   |

|                | 5.4.2          | LLWU         | configuration examples                           | 53   |

|                |                | 5.4.2.1      | Enabling pins and modules in the LLWU            | 53   |

|                |                | 5.4.2.2      | Module wake-up                                   | 54   |

|                |                | 5.4.2.3      | Pin wake-up                                      | 54   |

|                |                | 5.4.2.4      | LLWU port and module interrupts                  | 55   |

|                |                | 5.4.2.5      | Wake-up sequence                                 | 55   |

| 5.5            | Modu           | le operation | on in low-power modes                            | 57   |

| 5.6            | Mode           | transition   | requirements                                     | 59   |

| 5.7            | Source         | e of wake-   | -up, pins, and modules                           | 61   |

|                |                |              | Chapter 6<br>IOPORT module (Single Cycle I/O Por | rt)  |

| 6.1            | Using          | the single   | e cycle IOPORT module                            | 63   |

|                | 6.1.1 Overview |              | 63                                               |      |

|                |                | 6.1.1.1      | Introduction.                                    | 63   |

|                | 6.1.2          | Mapping      | g the IOPORT to GPIO registers                   | 63   |

|                |                | 6.1.2.1      | IOPORT module registers                          | 63   |

| 6.2            | Sampl          | e code usi   | ing the IOPORT in any run mode                   | 64   |

|                | 6.2.1          | IOPORT       | Γ code example                                   | 64   |

|                |                |              | Chapter 7 Direct Memory Access (DMA) Control     | ler  |

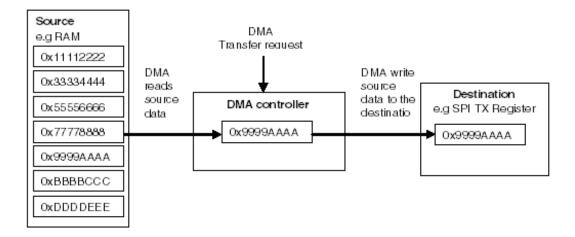

| 7.1            | DMA.           |              |                                                  | 67   |

|                | 7.1.1          | Overvie      | ·w                                               | 67   |

|                |                | 7.1.1.1      | Introduction                                     | 67   |

|                | 7.1.2          | DMA tr       | igger                                            | 69   |

|                |                | 7.1.2.1      | Trigger mode                                     | 69   |

| Sec | ction i | number Title                                       | Page |

|-----|---------|----------------------------------------------------|------|

|     | 7.1.3   | DMA multiplexer                                    | 70   |

|     | 7.1.4   | Transfer process.                                  | 71   |

|     |         | 7.1.4.1 Multiple transfer requests                 | 72   |

|     |         | 7.1.4.2 Asynchronous transfers                     | 73   |

|     | 7.1.5   | Configuration steps                                | 73   |

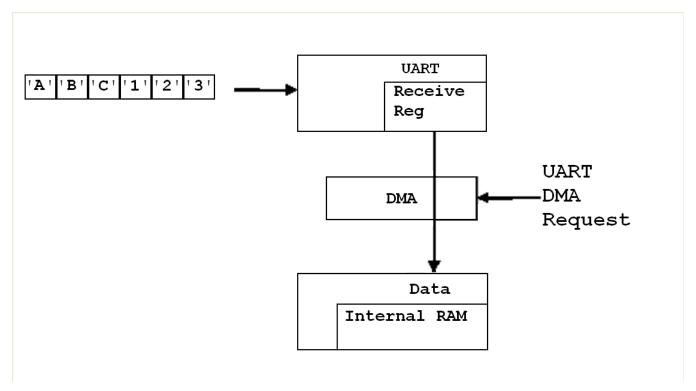

|     | 7.1.6   | Example—UART-gated DMA requests                    | 73   |

|     |         | 7.1.6.1 Requirements                               | 74   |

|     |         | 7.1.6.2 Module configuration                       | 74   |

|     |         | Chapter 8                                          |      |

|     |         | Universal asynchronous receiver/transmitter (UART) |      |

| 8.1 | Overv   | iew                                                | 77   |

| 8.2 | Introd  | uction                                             | 77   |

| 8.3 | Featur  | res                                                | 77   |

|     | 8.3.1   | UART clock.                                        | 78   |

|     | 8.3.2   | UART baud rate generation.                         | 78   |

|     | 8.3.3   | Receiver wake-up feature                           | 79   |

|     | 8.3.4   | Additional features.                               | 80   |

| 8.4 | Config  | guration examples                                  | 84   |

|     | 8.4.1   | Example 1: Polling/Interrupt mode of UART          | 84   |

|     | 8.4.2   | Example 2: Functionality of UART0 in VLPS mode     | 87   |

|     |         | Chapter 9<br>Universal Serial Bus OTG Module       |      |

| 9.1 | Introd  | uction                                             | 91   |

| 9.2 | Featur  | res                                                | 91   |

| 9.3 | USB o   | operation modes                                    | 91   |

| 9.4 | Voltag  | ge regulator operation modes                       | 92   |

| 9.5 | Modu    | le configuration                                   | 94   |

|     | 9.5.1   | Module dependencies.                               | 94   |

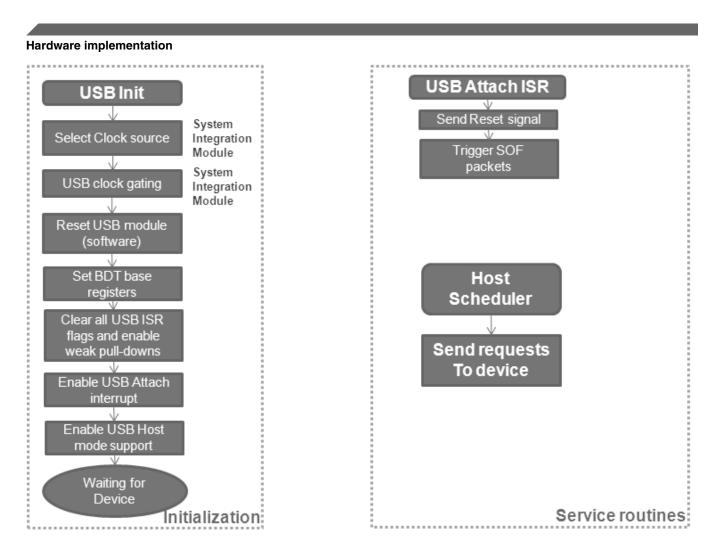

|     | 9.5.2   | USB initialization process                         | 94   |

| Sec   | ction nu | imber Title                                                                  | Page       |

|-------|----------|------------------------------------------------------------------------------|------------|

|       | 9.5.3    | Voltage regulator initialization                                             | 96         |

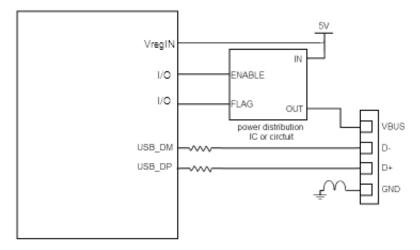

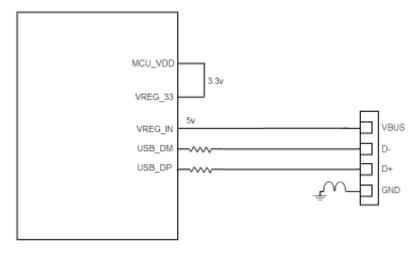

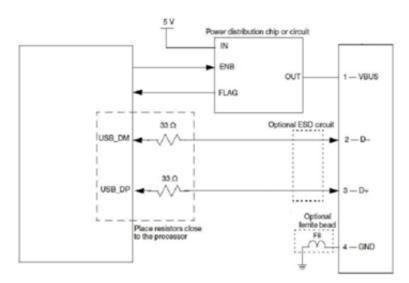

| 9.6   | Hardwar  | e implementation                                                             | 96         |

|       | 9.6.1    | Connection diagram                                                           | 96         |

|       | 9.6.2    | Components and placement suggestions                                         | 98         |

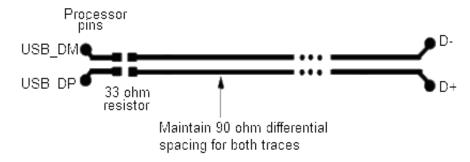

|       | 9.6.3    | ayout recommendations                                                        | 99         |

| 9.7   | Example  | code                                                                         | 100        |

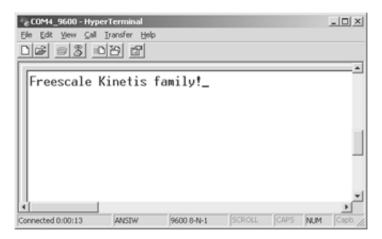

|       | 9.7.1    | Device code                                                                  | 100        |

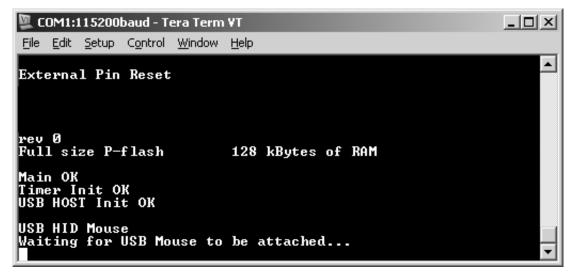

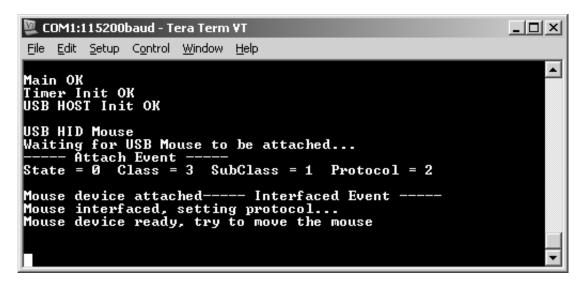

|       | 9.7.2    | Host code                                                                    | 101        |

|       |          | Chapter 10                                                                   |            |

|       |          | Touch Sense Input (TSI) Module                                               |            |

|       |          | ·                                                                            |            |

|       |          | ion                                                                          |            |

|       |          |                                                                              |            |

| 10.4  |          | iguration                                                                    |            |

|       |          | Configuration Example                                                        |            |

| 10.5  |          | 0.4.1.1 Code Example and Explanation                                         |            |

| 10.5  |          | PCB Routing and Placement                                                    |            |

|       | 10.5.1   |                                                                              | 113        |

| Using | g Low-F  | Chapter 11 cower Timer (LPTMR) to Schedule Analog-to-Digital Converter (ADC) | Conversion |

| 11.1  | Overvie  | V                                                                            | 115        |

|       | 11.1.1   | ntroduction                                                                  | 115        |

|       | 11.1.2   | Seatures                                                                     | 116        |

| 11.2  | Configur | ation example                                                                | 117        |

|       | 11.2.1   | PTMR-triggered single-ended ADC conversion                                   | 117        |

|       |          | 1.2.1.1 Turn on ADC and LPTMR clock gate                                     | 118        |

|       |          | 1.2.1.2 Configure SIM for ADC trigger                                        | 118        |

|       |          | 1.2.1.3 Configure the LPTMR                                                  | 118        |

|       |          | 1.2.1.4 Determine the ADC configuration                                      | 118        |

|       |          |                                                                              |            |

| Sec  | tion number       | Title                                        | Page |

|------|-------------------|----------------------------------------------|------|

|      | 11.2.1.5          | Using the ADC driver                         | 119  |

|      | 11.2.1.6          | Calibrate the ADC                            | 119  |

|      | 11.2.1.7          | Enable the LPTMR and ADC interrupt           | 119  |

|      | 11.2.1.8          | Start the LPTMR timer counting               | 120  |

|      | 11.2.1.9          | Handling LPTMR and ADC interrupt             | 120  |

|      | 11.2.2 ADC dev    | vice hardware implementation                 | 120  |

|      | 11.2.3 LPTMR      | device hardware implementation               | 120  |

| 11.3 | PCB design reco   | mmendations                                  | 121  |

|      | 11.3.1 Layout g   | uidelines                                    | 121  |

|      | 11.3.1.1          | General routing and placement                | 121  |

|      | 11.3.2 ESD/EM     | II considerations                            | 121  |

|      |                   | Chapter 12<br>Timer/PWM Module (TPM)         |      |

| 12.1 | Overview          |                                              | 123  |

| 12.2 | Introduction      |                                              | 123  |

| 12.3 | Features          |                                              | 123  |

|      | 12.3.1 TPM clo    | ck                                           | 124  |

|      | 12.3.2 Interrupt  | s and DMA                                    | 124  |

|      | 12.3.3 Modes of   | f operation                                  | 124  |

|      | 12.3.4 Initializa | tion of TPM                                  | 125  |

|      | 12.3.5 Updating   | g MOD and CnV                                | 125  |

|      | 12.3.6 TPM per    | iod                                          | 125  |

|      | 12.3.7 TPM trig   | gers                                         | 126  |

|      | 12.3.8 Addition   | al features                                  | 126  |

| 12.4 | Configuration ex  | amples                                       | 127  |

|      | 12.4.1 Example    | 1 – Edge Aligned PWM and Input Capture Mode  | 127  |

|      | 12.4.2 Example    | 2 – TPM functionality in low power stop mode | 131  |

# **Chapter 1 General System Setup (Software Considerations)**

#### 1.1 Software considerations

#### 1.1.1 Overview

This chapter provides a quick look at some of the general characteristics of the Kinetis L series of MCUs. This is a brief introduction of the operation of the devices and typical software initialization.

For more information, see the device-specific reference manual and data sheet.

#### 1.1.2 Code execution

The Kinetis L series features embedded Flash and SRAM memory for data storage and program execution.

## 1.1.3 Reset and booting

When the processor exits reset, it fetches the initial stack pointer (SP) from vector table offset 0 and the program counter (PC) from vector table offset 4. The initial vector table must be located in the flash memory at the base address (0x0000\_0000). However, the vector table can be relocated to SRAM after the boot-up sequence if desired. This device supports booting from internal flash and RAM. This device supports booting from internal flash with the reset vectors located at addresses 0x0 (initial SP\_main), 0x4 (initial PC), and RAM with the relocation of the exception vector table to RAM.

After fetching the stack pointer and program counter, the processor branches to the PC address and begins executing instructions.

#### Software considerations

For more information, see the "Reset and Boot" chapter of the device-specific reference manual.

#### 1.1.3.1 Device state during reset

With the exception of the SWD pins, during reset the digital I/O pins go to a disabled (high impedance) state with internal pullups/pulldowns disabled. Pins with analog functionality will default to their analog functions.

#### 1.1.3.2 Device state after reset

After reset, the digital I/O pins remain disabled until enabled by software. Also, interrupts are disabled and the clocks to most of the modules are off. The default clock mode after reset is FLL Engaged Internal (FEI) mode. In this mode, the system is clocked by the frequency-locked loop (FLL) using the slow internal reference clock as its reference. The watchdog timer is active; therefore it will need to be serviced, or disabled if debugging. The core clock, system clock, and flash clock are enabled after reset to support booting. Also, the flash memory controller cache and prefetch buffers are enabled.

## 1.1.4 Typical system initialization

The following is a summary of typical software initialization. The code snippets are taken from a "hello\_world" project written in IAR Embedded Workbench. This project is available in the Kinetis sample code found in the file KL25\_SC.exe which accompanies this guide.

## 1.1.4.1 Lowest level assembly routines

These routines are assembly source code found in the file crt0.s. The address of the start of this code is placed in the vector table offset 4 (initial program counter) so that it is executed first when the processor starts up. This is accomplished by labeling this section, exporting the label, and placing the label in the vector table. The vector table can be found in vectors.h. In this example the label used is \_\_startup.

## 1.1.4.1.1 Initialize general purpose registers

As a general rule, it is recommended to initialize the processor general purpose registers (R0-R7) to zero. One way of doing this is with the LDR instruction.

```

LDR

r0, =0

; Initialize the GPRs

LDR

r1, = 0

LDR

r2, =0

r3, = 0

LDR

r4, = 0

LDR

LDR

r5,=0

r6,=0

LDR

LDR

r7, = 0

```

#### 1.1.4.1.1.1 Unmask interrupts at ARM core

```

CPSIE i ; Unmask interrupts

```

#### 1.1.4.1.1.2 Branch to start of C initialization code

#### 1.1.4.2 Startup routines

These routines are C source code found in the files start.c and sysinit.c. This code provides general system initialization that may be adapted depending on the application.

#### 1.1.4.2.1 Disable watchdog

For code development and debugging, it is best to disable the watchdog. The COP can be disabled by clearing COPCTRL[COPT] in the SIM.

```

/* Disable the watchdog timer */

SIM COPC = 0x00;

```

#### 1.1.4.2.2 Initialize RAM

Depending on the application, the following steps may be required. First, copy the vector table from flash to RAM, copy initialized data from flash to RAM, clear the zero-initialized data section, and copy functions from flash to RAM.

## 1.1.4.2.3 Enable port clocks

To configure the I/O pin muxing options, the port clocks must first be enabled. This allows the pin functions to later be changed to the desired function for the application.

```

SIM_SCGC5 |= (SIM_SCGC5_PORTA_MASK | SIM_SCGC5_PORTB_MASK | SIM_SCGC5_PORTC_MASK | SIM_SCGC5_PORTD_MASK | SIM_SCGC5_PORTD_MASK | SIM_SCGC5_PORTE_MASK );

```

#### 1.1.4.2.4 Ramp system clock to selected frequency

The Multipurpose clock generator (MCG) provides several options for clocking the system. Configure the MCG mode, reference source, and selected frequency output based on the needs of the system.

#### 1.1.4.2.5 Enable pin interrupt

In this example, pin PTA4 is connected to a push button. An interrupt is generated when the button is pressed. A GPIO interrupt is used instead of an NMI interrupt because an edge-sensitive interrupt is preferred versus a level-sensitive interrupt. This ensures that one interrupt will occur per button press.

Interrupts need to be enabled in the ARM core, as described in the sections detailing NVIC.

```

/* Configure the PTA4 pin for its GPIO function */

PORTA_PCR4 = PORT_PCR_MUX(0x1); // GPIO is alt1 function for this pin

/* Configure the PTA4 pin for rising edge interrupts */

PORTA_PCR4 |= PORT_PCR_IRQC(0x9);

/* Initialize the NVIC to enable the specified IRQ */

enable_irq(30);

```

#### NOTE

To save space, the enable\_irq() function is not shown. See the interrupts section for details on how to enable the IRQ. Also, to save space, the interrupt service routine is not shown.

#### 1.1.4.2.6 Enable UART for terminal communication

See the section describing UART in this document for more information.

#### 1.1.4.2.7 Jump to start of main function for application

```

/* Jump to main process */

main();

```

# **Chapter 2 General System Setup (Hardware Considerations)**

#### 2.1 Hardware considerations

#### 2.1.1 Overview

This chapter will outline the best practices for hardware design when using the Kinetis L series MCUs. The designer must consider numerous aspects when creating the system so that performance, cost, and quality meet the end-user expectations. Performance usually implies high speed digital signalling, but it also applies to accurate sampling of analog signals. Cost is influenced by component selection, of which the PCB may be the most expensive element. Quality involves manufacturability, reliability, and conformance to industry or governmental standards.

Evaluation boards are great for evaluating the operation and performance of the many features of Freescale MCUs. However, evaluation systems are not ideal examples for implementation of robust system design techniques. This document will mention some of the hardware techniques found on the Freescale Tower Systems, and will give recommendations that are more appropriate to conventional systems that are not required to implement all of the feature options.

## 2.1.2 Floorplan

The organization of the printed circuit board (PCB) depends on many factors. Typically, there are connectors, mechanical components, high speed signals, low speed signals, switches, and power domains, among others, that need to be considered. While placement of connectors and some mechanical components (switches, relays, and so on) is critical to the end product's form, there are some basic recommendations that can significantly affect the electrical performance and electromagnetic compatibility (EMC) of the PCB assembly.

#### 2.1.2.1 Connectors

The PCB should be organized so that all of the connectors are along one edge of the board and away from the MCU. The concept here is to prevent placing the MCU in between connectors that can become effective radiators when cables are attached. This also keeps the MCU from being in the path of high energy transients that can shoot across the board from one connector to another. Connectors may be placed on adjacent edges of the PCB if necessary, but only when the MCU is not in a direct path between the connectors.

Connector locations should allow for placement of filter components. Noise must be suppressed at the connector, before it can propagate onto the PCB. For more information on this topic, see the input filtering section.

## 2.1.3 PCB routing considerations

This section covers critical power and filtering aspects of PCB layout.

## 2.1.3.1 Power supply routing

Routing of power and ground to digital systems is a topic that is discussed and debated in many textbooks and references. The basic concept is to ensure that the MCU and other digital components have a low impedance path to the power supply. The typical guidance that was given for one and two layer PCBs was to use wide traces and few layer transitions. The recommendations for today's high speed MCUs follow those given for high speed microprocessor systems – specifically, use planes for power and ground. This may raise the PCB cost, but the benefits of crosstalk reduction, reduction of RF emissions, and improved transient immunity can be realized with lower overall production and maintenance costs.

In general, the ground routing should take precedence over any other routing. Ground planes or traces should never be broken by signals. For packages with leads, like the LQFP, a ground plane directly below the MCU package is recommended to reduce RF emissions and improve transient immunity. All of the VSS pins of the MCU should be tied to a ground plane. Ground traces from a plane should be kept as short as possible as they are routed to circuitry on signal layers (top and bottom). Power planes may be broken to supply different voltages. All of the VDD pins of the MCU should be tied to

the proper power plane. Power traces from the planes should be kept as short as possible as they are routed to circuitry, such as pullups, filters, other logic and drivers, on the top and bottom layers. More information is given in the PCB layer stack-up section below.

## 2.1.3.2 Power supply decoupling and filtering

Bypass capacitors, while also called decoupling capacitors, are the storage elements that provide the instantaneous energy demanded by the high speed digital circuits.

Power supply bypass capacitors must be placed close to the MCU supply pins. The basic concept is that the bypass capacitor provides the instantaneous current for every logic transition within the MCU. Fortunately, each Kinetis MCU has a low voltage internal regulator for the MCU core logic, therefore the abrupt current demands of the internal high speed logic are not as critical. However, external signals demand energy from the power rails when they transition from one logic level to the other. The bypass capacitors provide the local filtering so that the effects of the external pin transitions are not reflected back to the power supply, which causes RF emissions.

The basic rule of placing bypass capacitors as close as possible to the MCU is still appropriate. The idea is to minimize the loop created by the capacitor between the VDD and VSS pins. The implementation of this rule depends on the number of mounting layers, how the supplies are routed, and the physical size of the capacitors:

- Number of mounting layers PCBs with components mounted only on the top side will have a significant limitation on how close the bypass caps can be located due to the number of components that require space. PCBs that have components mounted on both sides of the PCB allow closer placement of the bypass capacitors.

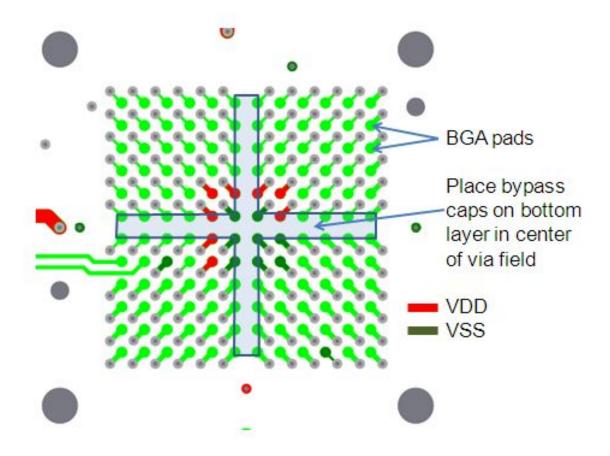

- Supply routing With the Ball Grid Array (BGA) package, all of the VDD/VSS pairs are routed to other layers under the package. This allows easier attachment of the VDD and VSS pins to the power and ground planes within those layers. The bypass capacitors can be placed in the area below the MCU, with connections very close to the power pins. See the following figure.

Figure 2-1. K60 TWR board top layer BGA pad arrangement

• Supply routing – For Quad Flat Pack (QFP) packages, the power supply pins may be supplied radially to the MCU using traces rather than from planes. Although it is adequate to place the bypass capacitors close to the VDD and VSS pins on the traces leading to the MCU, it is better to have the ground side of the bypass capacitor tied to the ground plane (through a via and short trace) close to the VSS pin and the VDD side tied to the power plane (through a via and short trace) close to the VDD pin.

#### 2.1.3.3 Oscillators

The Kinetis MCU starts up with an internal digitally controlled oscillator (DCO) to control the bus clocking, and then software can be used to enable an external oscillator if desired. The external oscillator for the multipurpose clock generator (MCG) can range from a 32.768 kHz crystal up to a 32 MHz crystal or ceramic resonator.

#### 2.1.3.3.1 MCG oscillator

The high speed oscillator that can be used to source the MCG module is very versatile. The component choices for this oscillator are detailed in the device-specific reference manual. The placement of this crystal or resonator is described here.

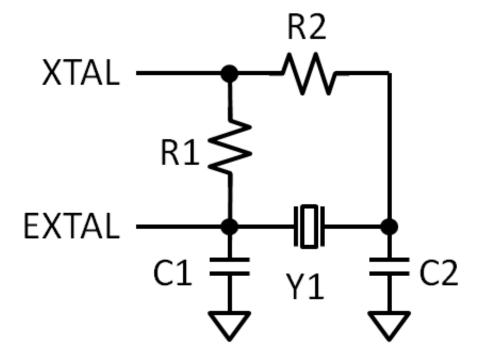

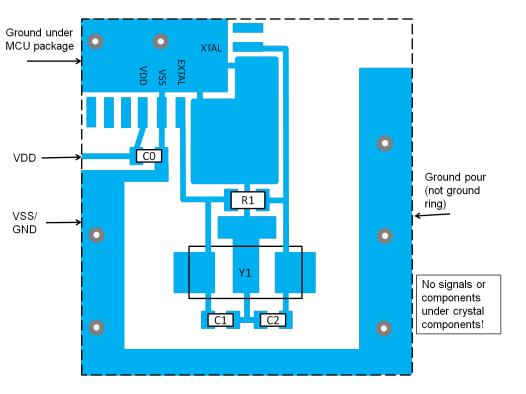

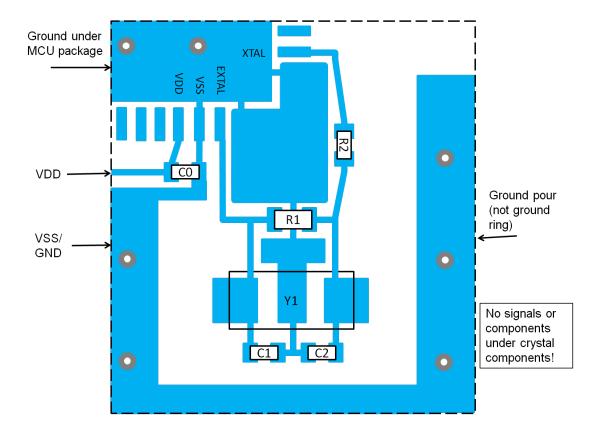

The EXTAL and XTAL pins are located on the outside pad ring of the BGA package and on corner pins of the LQFP/QFN package. This allows room for placement and routing of the crystal or resonator on the top layer, close to the MCU. The feedback resistor and load capacitors, if needed, can be placed on the top layer as well. See Figure 2-2, Figure 2-3, and Figure 2-4.

Note that the low power modes of this oscillator do not require a feedback resistor, and may not require external load capacitors. See the device-specific reference manual for details. This makes it as simple as possible because only one component has to be placed and routed. Low power oscillators are more susceptible to interference by system generated noise, therefore the guidelines for crystal routing are important.

The crystal or resonator must be located close to the MCU. No signals of any kind should be routed on the layer directly below the crystal. The load capacitors and ground of the crystal package must be connected to a single ground trace coming from the closest VSS pin or the recommended ground under the MCU. An unbroken ground plane on the layer directly below the crystal is recommended. A ground pour must be placed around the crystal and its load components to protect it from crosstalk from adjacent signals on the mounting layer.

Figure 2-2. Typical crystal circuit

Figure 2-3. Crystal layout for low power oscillator

Figure 2-4. Crystal layout for high power oscillator Kinetis L Peripheral Module Quick Reference, Rev. 0, 09/2012

#### 2.1.3.4 General filtering

General purpose I/O pins should have adequate isolation and filtering from transients.

#### 2.1.3.4.1 RESET\_b and NMI\_b

The RESET\_b pin, if enabled, should have a 100 nF capacitor close to the MCU for transient protection. The NMI\_b pin, if enabled, must not have any capacitance connected to it. Each pin, when enabled as their default function, has a weak internal pullup, but an external  $4.7~\mathrm{k}\Omega$  to  $10~\mathrm{k}\Omega$  pullup is recommended. As with power pin filtering, it is recommended to minimize the ground loop for the capacitor and the VDD loop for the pullup resistor for these pins.

The RESET\_b pin also has a configurable digital filter to reject potential noise on this input after power-up. The configuration bits are located in the RCM\_RPFC register. While use of this filter may negate the need for the pullup and capacitor mentioned above, it is still recommended to use external filtering in electrically noisy environments.

#### 2.1.3.4.2 General purpose I/O

General purpose inputs, such as low speed inputs, timer inputs, and signals from off-board should have low pass filters (series resistor and capacitor to ground) to prevent data corruption due to crosstalk or transients. The filter capacitor should be placed close to the MCU pin, while the resistor can be placed closer to the source.

Inputs that come from connectors should have low pass filtering at the connector to prevent noise from propagating onto the PCB. This requires a robust ground structure around the connector. Series resistors for signals that come from off-board should be placed as close to the connector as possible. A filter cap closer to the MCU input pin may be required if the signal trace length is very long and can pick up noise from other circuits.

Output pins must not have any significant capacitance placed close to the MCU. These signals can have capacitors at the load or connector to minimize radiated emissions if necessary.

## 2.1.3.4.3 Analog inputs

Analog inputs should also have low pass filters. The challenge with analog inputs, especially for high resolution analog-to-digital conversions, is that the filter design needs to consider the source impedance and sample time rather than a simple cutoff frequency. This topic cannot be discussed in detail here, but the general concept is that fast sample

#### Hardware considerations

times will require smaller capacitor values and source impedances than slow sample times. Higher resolution inputs may require smaller capacitor values and source impedances than lower resolution inputs.

In general, capacitor values can range from 10 pF for high speed conversions to 1 uF for low speed conversions. Series resistors can range from a few hundred Ohms to 10 k $\Omega$ .

## 2.1.4 PCB layer stack-up

The Kinetis L series MCUs are high speed integrated circuits. Care must be taken in the PCB design to ensure that fast signal transitions, such as rise/fall times and continuous frequencies, do not cause RF emissions. Likewise, transient energy that enters the system needs to be suppressed before it can affect the system operation (compatibility). The guidance from high speed PCB designers is to have all signals routed within one dielectric (core or prepreg) of a return path, which usually is a ground plane on a multilayer PCB and an adjacent ground on a two layer PCB. This allows return currents to predictably flow back to the source without affecting other circuits, which is the primary cause of radiated emissions in electronic systems. This approach requires full planes within the PCB layer stack and partial planes (copper pours) on signal layers where possible. All ground planes and ground pours must be connected with plenty of vias. Likewise, all "like" power planes and power pours must be connected with plenty of vias.

#### Recommended layer stackups:

#### 4-Layer PCB A:

Layer 1 (top – MCU location)—Ground plane and pads for top mounted components, no signals

Layer 2 (inner)—Signals and power plane

Thick core

Layer 3 (inner)—Signals and power plane

Layer 4 (bottom)—Ground plane and pads for bottom mounted components, no signals

## 4-Layer PCB B:

Layer 1 (top – MCU location)—Signals and poured power

Layer 2 (inner)—Ground plane

Thick core

Layer 3 (inner)—Ground plane

Layer 4 (bottom)—Signals and poured power

## 6-Layer PCB A:

Layer 1 (top – MCU)—Power plane and pads for top mounted components, no signals

- Layer 2 (inner)—Signals and ground plane

- Layer 3 (inner)—Power plane

- Layer 4 (inner)—Ground plane

- Layer 5 (inner)—Signals and power plane

- Layer 6 (bottom)—Ground plane and pads for bottom mounted components, no signals

#### 6-Layer PCB B:

- Layer 1 (top MCU)—Signals and power plane

- Layer 2 (inner)—Ground plane

- Layer 3 (inner)—Signals and power plane

- Layer 4 (inner)—Ground plane

- Layer 5 (inner)—Power plane

- Layer 6 (bottom)—Signals and ground plane

#### 6-Layer PCB C:

- Layer 1 (top MCU)—Signals and power plane

- Layer 2 (inner)—Ground plane

- Layer 3 (inner)—Signals and power plane

- Layer 4 (inner)—Signals and ground plane

- Layer 5 (inner)—Power plane

- Layer 6 (bottom)—Signals and ground plane

#### 8-Layer PCB A:

- Layer 1 (top MCU)—Signals

- Layer 2 (inner)—Ground plane

- Layer 3 (inner)—Signals

- Layer 4 (inner)—Power plane

- Layer 5 (inner)—Ground plane

- Layer 6 (inner)—Signals

- Layer 7 (inner)—Ground plane

- Layer 8 (bottom)—Signals

## 8-Layer PCB B:

- Layer 1 (top MCU)—Signals and power plane

- Layer 2 (inner)—Ground plane

- Layer 3 (inner)—Signals and power plane

- Layer 4 (inner)—Ground plane

- Layer 5 (inner)—Power plane

- Layer 6 (inner)—Signals and ground plane

- Layer 7 (inner)—Power plane

- Layer 8 (bottom)—Signals and ground plane

#### Kinetis L Peripheral Module Quick Reference, Rev. 0, 09/2012

#### Other module hardware considerations

#### 8-Layer PCB C:

Layer 1 (top – MCU)—Signals and ground plane

Layer 2 (inner)—Power plane

Layer 3 (inner)—Ground plane

Layer 4 (inner)—Signals

Thick core

Layer 5 (inner)—Signals

Layer 6 (inner)—Ground plane

Layer 7 (inner)—Power plane

Layer 8 (bottom)—Signals and ground plane

#### 8-Layer PCB D:

Layer 1 (top – MCU)—Signals and ground plane

Layer 2 (inner)—Power plane

Layer 3 (inner)—Ground plane

Layer 4 (inner)—Signals and power plane

Thick core

Layer 5 (inner)—Signals and power plane

Layer 6 (inner)—Ground plane

Layer 7 (inner)—Power plane

Layer 8 (bottom)—Signals and ground plane

In general, avoid placing one signal layer adjacent to another signal layer.

#### 2.1.5 Other module hardware considerations

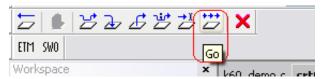

## 2.1.5.1 Debug interface

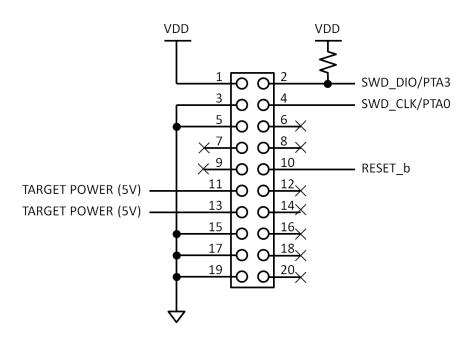

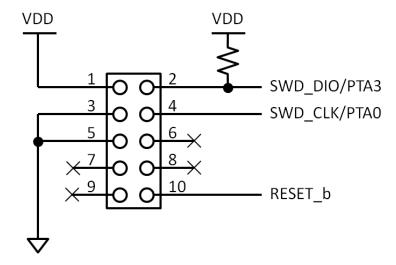

The Kinetis L series MCUs use the Cortex Debug interfaces for debugging and programming. The 19-pin Cortex Debug interfaces provides connections for Serial Wire debugging, as well as target power. The 9-pin Cortex Debug interfaces provides connections for Serial Wire debugging only. Figure 2-5 shows the 20-pin header implementation with 19 pins populated. Figure 2-6 shows the 10-pin header implementation with 9 pins populated as used on the TWR system and Freedom boards.

Figure 2-5. 20-pin debug interface

Figure 2-6. 10-pin debug interface

The debug signals are multiplexed with general purpose I/O pins, therefore some signals will require proper biasing to select the operating mode. The SWD\_CLK pin has an internal pull down device and SWD\_DIO has an internal pull up device. The connectors for this interface are keyed dual row 0.050" centered headers. When implementing either of these headers on a target system, pin 7 must be depopulated to use the 19-pin or 9-pin adapters from the debug tool. The Samtec part numbers for these connectors are:

- FTSH-110-01-L-DV-K 20-pin keyed connector

- FTSH-105-01-L-DV-K 10-pin keyed connector

- FTSH-110-01-L-DV 20-pin connector, no key

- FTSH-105-01-L-DV 10-pin connector, no key

This interface is useful during the development phase of a project. The header may not need to be populated in the production phase of the project, but the PCB pads should be kept available for future debugging purposes.

# **Chapter 3 Nested Vector Interrupt Controller (NVIC)**

#### **3.1 NVIC**

#### 3.1.1 Overview

This chapter shows how the NVIC is integrated into the Kinetis MCUs and how to configure it and set-up module interrupts. It also demonstrates the steps to set the interrupts for the desired peripheral and how to locate the vector table from flash to RAM.

#### 3.1.1.1 Introduction

The NVIC is a standard module on the ARM Cortex M series. This module is closely integrated with the core and provides very low latency entering and exiting an interrupt service routine (ISR). It takes 15 cycles to exit an ISR, unless the exit from the interrupt is into another pending ISR. In this case, the MCU tail-chains and the exit and re-entry takes 11 cycles.

The NVIC provides four different interrupt priorities which can be used to control the order in which interrupts must be serviced. Priorities are 0-3, with 0 receiving the highest priority. For example, in a motor-control application, if a timer interrupt and UART occur simultaneously, the timer interrupt that moves the motor is more critical than the UART interrupt receiving a character. The timer priority must be set higher than the UART.

#### **3.1.1.2** Features

On Kinetis L series MCUs the NVIC provides up to 48 interrupt sources including 16 that are core specific. It also implements up to four priority levels that are fully programmable. The NVIC uses a vector table to manage the interrupts. This vector table can be stored in either flash or RAM, depending on the application.

Address **IRQ** Vector Source module Source description ARM Core System Handler Vectors 0x0000 0000 0 ARM core Initial stack pointer 1 ARM core Initial program Counter 2 ARM core Non-maskable Interrupt (NMI) 3 ARM core Hard fault **SVCall** 11 ARM core 12 14 ARM core Pendable request for system service 15 ARM core System tick timer(SysTick)

Table 3-1. Core exceptions

## 3.1.2 Configuration examples

The NVIC is easy to configure, as demonstrated in the following examples. The first example shows how to configure the NVIC for a module, using the low power timer (LPTMR) as a base. The second example shows how to locate the vector table from the flash to RAM.

#### 3.1.2.1 Configuring the NVIC

Configuring the NVIC for the specific module involves writing three registers: NVIC Set Enable Register (NVICSERx), NVIC Clear Pending Register (NVICCPRx), and NVIC Interrupt Priority (NVICIPxx). After the NVIC is configured and the desired peripheral has its interrupts enabled, the NVIC serves any pending request from that module by going to the module's ISR.

## 3.1.2.1.1 Code example and explanation

This example shows how to set up the NVIC for a specific module, using the LPTMR.

The steps to configure the NVIC for this module are:

1. Identify the vector number and the IRQ number of the module from the vector table in the device-specific reference manual in the section *Interrupt Channel Assignments*. For the LPTMR the vector is 44.

Table 3-2. LPTMR vector

| Address     | Vector | IRQ | Source Module | Source<br>Description |

|-------------|--------|-----|---------------|-----------------------|

| 0x0000_00A8 | 42     | 26  | TSI           |                       |

| 0x0000_00AC | 43     | 27  | MCG           |                       |

| 0x0000_00B0 | 44     | 28  | LPTMR         |                       |

- 2. Determine which NVICSERx register contains the IRQ. Each NVICSERx register contains 32 IRQs. Therefore, the NVICSER0 can enable from IRQ 0 to IRQ 31. In this example, NVICSER0 is used, and the LPTMR IRQ is 28. The NVICCPRx uses the same number, in this case, NVICCPR2.

- 3. To find out which bit to set, perform a modulo operation dividing the IRQ number by 32. This number is used to enable the interrupt on NVICSER0 and to clear the pending interrupts from NVICCPR0.

Example:

LPTMR BIT =  $28 \mod 32$

LPTMR BIT = 28

4. At this point, the interrupt for the LPTMR can be configured:

```

NVICICPR0 = (1<<28);  //Clear any pending interrupts on LPTMR

NVICISER0 = (1<<28);  //Enable interrupts from LPTMR module</pre>

```

5. Next, set the interrupt priority level. This is application dependent. On Kinetis L-Series MCUs there are four different priority levels. To set the priority, write to the NVICIPxx register; the "xx" represents the IRQ number, which is NVICIP85 in this example. Note the most significant nibble is used to set up the priority, the lower nibble is reserved and reads as zero. The LPTMR example sets the priority to 3:

```

NVIC_IPR7 = 0x03; //Set Priority 3 to the LPTMR module

```

- 6. After the NVIC registers are set up, finish the peripheral configuration that must enable the interrupt.

- 7. In the ISR, clear the peripheral interrupt flag and read back the status register to avoid re-entrance. For this example:

```

void vfnLPTMR_ISR (void)

{

```

#### 3.1.2.2 Relocating the vector table

Some applications need the vector table to be located in RAM. For example in an RTOS implementation, the vector table needs to be in RAM, which allows the Kernel to install ISRs by modifying the vector table during runtime.

The NVIC provides a simple way to reallocate the vector table. The user needs to set up the Vector Table Offset Register (VTOR) with the address offset for the new position.

If you plan to store the vector table in RAM, you must first copy the table from the flash to RAM. Also note that in some low power modes, a portion of the RAM will not be powered, which can lead to a vector table corruption. In this case, locate the vector table in the flash prior to entering a low power mode.

#### 3.1.2.2.1 Code example and explanation

The CM0+ core adds support for a programmable Vector Table Offset Register (VTOR) to relocate the exception vector table. This device supports booting from internal flash. The vector table is initially in flash. If the vector table is needed in RAM, move it in this manner:

1. Copy the entire vector table from flash to RAM. The linker command file labels are useful in this step. Refer to the following sample code:

```

/*Address for VECTOR_TABLE and VECTOR_RAM come from the linker file*/

extern uint32 __VECTOR_TABLE[];

extern uint32 __VECTOR_RAM[];

/* Copy the vector table to RAM */

if (_VECTOR_RAM != __VECTOR_TABLE)

{

for (n = 0; n < 0x104; n++)

_VECTOR_RAM[n] = __VECTOR_TABLE[n];

}</pre>

```

2. After the table has been copied, set the proper offset for the VTOR register:

```

/* Point the VTOR to the new copy of the vector table */

write_vtor((uint32)__VECTOR_RAM);

```

It is important to follow these steps in order, to ensure that there is always a valid vector table.

# **Chapter 4 Clocking System**

## 4.1 Clocking

#### 4.1.1 Overview

This chapter will discuss the clocking system and the multipurpose clock generator (MCG) module. Examples will provide an overview of how to switch between the MCG modes and specifically how to enable the on-chip PLL for high-speed operation. Clock selection options will be discussed for the RTC.

#### 4.1.2 Features

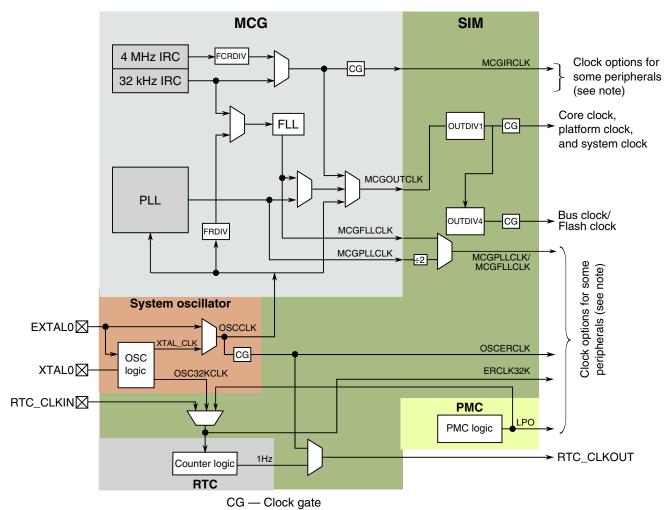

An example of the clocking system is summarized in the following figure. Not all clock sources will be available on specific devices. Refer to the individual device reference manual for full details of the available clock sources.

Note: See subsequent sections for details on where these clocks are used.

Figure 4-1. Clock distribution diagram

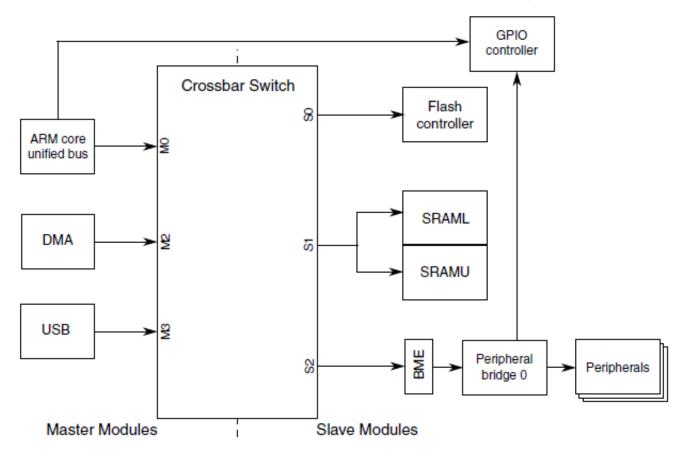

The system level clocks are provided by the MCG. The MCG consists of:

- Two individually trimmable internal reference clocks (IRC), a slow IRC with a frequency of ~32 kHz and a fast IRC with a frequency of ~4 MHz, which can be reduced by means of the FCRDIV divider

- Frequency locked loop (FLL) using the slow IRC or an external source as the reference clock

- Phase locked loop (PLL) using an external source as the reference clock (the PLL is not available on all devices

- Auto trim machine (ATM) to allow both of the IRCs to be trimmed to a custom frequency using an externally-generated reference clock

The clocks provided by the MCG are summarized as follows:

- MCGOUTCLK The main system clock used to generate the core, bus, and memory clocks. It can be generated from one of the on-chip reference oscillators, the on-chip crystal/resonator oscillator, an externally generated square wave clock, the FLL, or the PLL.

- MCGFLLCLK The output of the FLL and is available any time the FLL is enabled.

- MCGPLLCLK The output of the PLL and is available any time the PLL is enabled.

- MCGIRCLK The output of the selected IRC. The selected IRC will be enabled whenever this clock is selected.

In addition to the clocks provided by the MCG, there are three other system level clock sources available for use by various peripheral modules:

- OSCERCLK The clock provided by the system oscillator and is the output of the oscillator or the external square wave clock source.

- ERCLK32K The output of the system oscillator if it is configured in low power mode at 32 kHz, the external RTC\_CLKIN path or the low power oscillator (LPO).

- LPO The output of the low power oscillator. It is an on-chip, very low power oscillator with an output of approximately 1 kHz that is available in all run and low power modes except VLLSO.

## 4.1.3 Configuration examples

The MCG can be configured in one of several modes to provide a flexible means of providing clocks to the system for a wide range of applications.

After exiting reset, or recovering from a very low leakage state, the MCG will be in FLL engaged internal (FEI) mode with MCGCLKOUT at 20.97 MHz, assuming a factory trimmed slow IRC frequency of 32.768 kHz. If a different MCG mode is required, the MCG can be transitioned to that mode under software control.

It is only possible to transition directly to certain MCG modes. Refer to the individual device reference manual for details on this. It may be required to transition through several modes to reach the desired MCG mode. When transitioning from one clock mode to another, you must ensure that you have fully entered that mode before moving to the next mode. The mcg.c file within the sample code contains examples of how to perform all the individual clock mode transitions. The pll\_init function combines three of these individual transitions into one function. The specific MCG register operations will be discussed below.

In this example, the PLL will be configured to use an external 8 MHz clock from the crystal oscillator and generate a 96 MHz output frequency. This is a typical configuration when the USB module is being used. The MCGPLLCLK frequency is half the PLL

#### Clocking

frequency. When it is desired to provide the USB clock of 48 MHz, the PLL must be set at 96 MHz. The MCG is configured to minimize PLL jitter, that is,maximum PLL frequency with the minimum multiplication factor.

The first step is to move from the default FEI mode to the FLL bypassed external mode (FBE).

```

// first configure the oscillator settings in the MCG_C2 register

// the RANGE value is determined by the external frequency. Since the RANGE

// parameter affects the FRDIV divide value it still needs to be set correctly even

// if an external clock is being used

MCG_C2 = (MCG_C2_RANGE0(1) | MCG_C2_EREFS0_MASK);

// The FRDIV is determined by the reference clock frequency and should be set to

// keep the FLL ref clock frequency within the correct range. For 8MHz ref this

// needs to be a divide of 256

// The CLKS bits must be set to b'10 to select the external reference clock

// Clearing IREFS selects and enables the external oscillator

MCG_C1 = (MCG_C1_CLKS(2) | MCG_C1_FRDIV(3));

// When the external oscillator is used need to wait for OSCINIT to set

for (i = 0 ; i < 20000 ; i++)

// jump out early if OSCINIT sets before loop finishes

if (MCG S & MCG S OSCINITO MASK) break;

// wait for Reference clock Status bit to clear

for (i = 0 ; i < 2000 ; i++)

// jump out early if IREFST clears before loop finishes

if (!(MCG S & MCG S IREFST MASK)) break;

// Wait for clock status bits to show clock source is ext ref clk

for (i = 0 ; i < 2000 ; i++)

// jump out early if CLKST shows EXT CLK selected before loop finishes

if (((MCG_S & MCG_S_CLKST_MASK) >> MCG_S_CLKST_SHIFT) == 0x2) break;

// Now in FBE

```

After making changes to clock selection bits or enabling either the oscillator of PLL, the appropriate status bits must be verified before continuing. A simple "while" loop is not recommended for polling the status bits. If for some reason the bit being checked does not update, the "while" loop will never exit, unless a timeout mechanism is used. A "for" loop is used here to perform this function. If a timeout is generated, a decision can be made about what to do depending on the status bits that failed to update. For example, if the oscillator does not start due to a damaged PCB trace, the decision to continue with an internal-only clocking mode can be made with an appropriate indication to the user or a central monitoring station.

When an external clock is being used, it is recommended to enable the clock monitor. This can be configured to generate an interrupt or a system reset. This is performed by the statement:

```

MCG C6 |= MCG C6 CME0 MASK;

```

The next step is to enable the PLL, and move to PLL bypassed external mode. This allows the PLL to lock while still clocking the system from the external reference clock.

```

// Configure MCG C5 to set the PLL reference clock at the right frequency

MCG C5 \mid = MCG C5 PRDIVO(1);

//set PLL ref divider to divide by 2

// Configure MCG C6 to set the PLL multiplier and enable the PLL

// The PLLS bit \overline{i}s set to enable the PLL, MCGOUT still sourced from ext ref clk

temp_reg = MCG_C6; // store present C6 value (as CME0 bit was previously set)

temp_reg &= ~MCG_C6_VDIV0_MASK; // clear VDIV settings

temp_reg |= MCG_C6_PLLS_MASK | MCG_C6_VDIV0(0); // write new VDIV and enable PLL

MCG_C6 = temp_reg; // update MCG_C6

// wait for PLLST status bit to set

for (i = 0 ; i < 2000 ; i++)

// jump out early if PLLST sets before loop finishes

if (MCG_S & MCG_S_PLLST_MASK) break;

// Wait for LOCK bit to set

for (i = 0 ; i < 4000 ; i++)

// jump out early if LOCK sets before loop finishes

if (MCG_S & MCG_S_LOCKO_MASK) break;

// now in PBE

```

After the PLL is enabled and locked, the MCGOUTCLK can be switched to the PLL output. Before switching to this higher frequency clock you must set the system clock dividers to keep the system clock frequencies within specifications.

```

// set the core clock divider to divide by 2

// set the bus clock divider to divide by 2 (bus clock is sourced from core clock)

SIM_CLKDIV1 = (SIM_CLKDIV1_OUTDIV1(1) | SIM_CLKDIV1_OUTDIV4(1) );

```

Now it is possible to switch to the PLL.

```

// clear CLKS to switch CLKS mux to select the PLL as MCGCLKOUT

MCG_C1 &= ~MCG_C1_CLKS_MASK;

// Wait for clock status bits to update

for (i = 0 ; i < 2000 ; i++)

{

// jump out early if CLKST = 3 before loop finishes

if (((MCG_S & MCG_S_CLKST_MASK) >> MCG_S_CLKST_SHIFT) == 0x3) break;

}

// Now in PEE

```

# 4.1.3.1 Configuring the RTC clock source

The RTC does not have a dedicated oscillator, but the clock source can be selected from one of three options:

- The system oscillator when it is configured for 32 kHz, low power operation (OSC32KCLK)

- The RTC\_CLKIN pin

- The LPO

The time keeping function of the RTC and the RTC\_CLKOUT frequency will be correct only when a 32.768 kHz clock source is used. The LPO can be used only for a timed wake up function. The OSC32KCLK is only available when an external 32 kHz crystal is used and the oscillator low power mode is selected (MCG\_C2[HGO0] = 0). The OSC32KCLK is available in all power modes except VLLS0. In VLLS0, the only clock source that is available for the RTC, and therefore a timed wake up, is the RTC\_CLKIN selection.

To select the RTC\_CLKIN in path, the GPIO mux must be set to the GPIO selection and SIM\_SOPT1[OSC32KSEL] set to select the RTC\_CLKIN path.

```

// Ensure PTC1 is configured as RTC input clock

PORTC_PCR1 = ~PORT_PCR_MUX_MASK;

PORTC_PCR1 = PORT_PCR_MUX(1);

// RTC_CLKIN selected as the ERCLK32K

SIM SOPT1 |= SIM_SOPT1_OSC32KSEL(2);

```

To select the OSC32KCLK the oscillator must be configured by means of the RTC\_CR register and the SIM\_SOPT1[OSC32KSEL] field set to select the OSC32KCLK.

```

// Enable the oscillator by means of the RTC_CR register

// Note that if it is desired to use the the internal load capacitors, they MUST be

// selected in the same register using the SCxP bits

OSC_CR |= OSC_CR_OSCE_MASK; // set the oscillator enable bit

// Oscillator selected as the ERCLK32K

SIM_SOPT1 &= ~SIM_SOPT1_OSC32KSEL_MASK; // Clear the OSC32KSEL field to select osc

```

Always enable the oscillator using the RTC\_CR register rather than by configuring the MCG and OSC registers. The RTC registers are only reset during power on reset, whereas the MCG and OSC registers are reset by any reset and during VLLSx recovery. This allows the RTC to retain time keeping during any reset except POR.

To select the LPO as the RTC clock source only the SIM\_SOPT1[OSC32KSEL] must be set to select the LPO.

```

// LPO selected as the ERCLK32K

SIM_SOPT1 |= SIM_SOPT1_OSC32KSEL(3);

```

## 4.1.4 Additional clock options

The Kinetis L series offers three new clock options. These allow for additional current savings by automatically shutting down system level clocks. These options are briefly described below. Refer to the device reference manual for further details.

#### 4.1.4.1 Compute operation

Compute operation (CPO) is a means of reducing the the current consumption in RUN or VLPR modes. Access to the peripherals is not possible and only the platform resources are available, including the MCM, NVIC, IOPORT, and SysTick. CPO is intended to be used in computationally intensive applications when peripheral access is not required. Although the IOPORT is accessible, the GPIO input state cannot be read, but the GPIO output state can be controlled. Any off platform peripheral access will result in a bus error.

Asynchronous interrupts and DMA transfer requests are still available when using CPO. A DMA request will automatically exit CPO and re-enter CPO when it has completed. Most peripheral interrupts will require CPO to be exited before servicing them.

To enter or exit CPO simply requires that CPOREQ be set/cleared, and CPOACK be checked that it has updated appropriately.

```

/* Enter compute operation */

MCM_CPO |= MCM_CPO_CPOREQ_MASK; //

while(!(MCM_CPO & MCM_CPO_CPOACK_MASK));

/* Exit compute operation */

MCM_CPO &= ~MCM_CPO_CPOREQ_MASK;

while (MCM_CPO & MCM_CPO_CPOACK_MASK);

```

#### 4.1.4.2 Partial stop

There are two partial stop options: Partial Stop 1 (PSTOP1) and Partial Stop 2 (PSTOP2).

In PSTOP1, the system enters STOP mode with the core, system, and bus clocks gated off but keeps the MCG clocks running and the PMC remains on. This allows for a faster wakeup at the expense of higher power consumption.

In PSTOP2, only the core and system clocks are gated off, and the MCG clocks and PMC remain on. This allows peripherals which are clocked by the bus clock to remain active.

The partial stop options are enabled by means of setting the appropriate STOP level in the SMC\_STOPCTRL register.

```

/* Enter normal STOP */

SMC STOPCTRL = SMC STOPCTRL PSTOPO(0); // this also clears the other register bits

```

#### Clocking

```

/* Enter PSTOP1 */

SMC_STOPCTRL = SMC_STOPCTRL_PSTOPO(1); // this also clears the other register bits

/* Enter PSTOP2 */

SMC_STOPCTRL = SMC_STOPCTRL_PSTOPO(2); // this also clears the other register bits

```

# 4.1.5 Clocking system device hardware implementation

It is possible to provide all the system level clocks from internal sources. However, if the PLL is to be used or an accurate reference clock is required, an external clock must be provided. This can be from an externally generated clock source that provides a square wave clock, or it can be from an internal oscillator using an external crystal or resonator.

The main system oscillator can be configured in various ways depending on the crystal frequency and mode being used. Refer to the device-specific reference manual for details. When the oscillator is configured for low power, an integrated oscillator feedback resistor is provided. The oscillator also has programmable internal load capacitors when it is configured as a 32kHz oscillator (RANGE = 0). The internal crystal load capacitors are selectable in software to provide up to 30 pF, in 2 pF increments, for each of the EXTAL and XTAL pins. This provides an effective series capacitive load of up to 15 pF. The parasitic capacitance of the PCB should also be included in the calculation of the total crystal load. The combination of these two values will often mean that no external load capacitors are required when using a 32 kHz crystal.

If either of the oscillator pins are not being used, they may be left unconnected in their default reset configuration or may be used as GPIO.

# 4.1.6 Layout guidelines for general routing and placement

Use the following general routing and placement guidelines when laying out a new design. These guidelines will help to minimize electromagnetic compatibility (EMC) problems:

- To minimize parasitic elements, surface mount components must be used where possible

- All components must be placed as close to the MCU as possible.

- If external load capacitors are required, they must use a common ground connection shared in the center

- If the crystal, or resonator, has a ground connection, it must be connected to the common ground of the load capacitors

- Where possible:

- Keep high-speed IO signals as far from the EXTAL and XTAL signals as possible

- Do not route signals under oscillator components on same the layer or layer below

- Select the functions of pins close to EXTAL and XTAL to have minimal switching to reduce injected noise

#### 4.1.7 References

The following list of application notes associated with crystal oscillators are available on the Freescale website at www.freescale.com. They discuss common oscillator characteristics, potential problems, and troubleshooting guidelines:

- AN1706: Microcontroller Oscillator Circuit Design Considerations

- AN1783: Determining MCU Oscillator Start-Up Parameters

- AN2606: Practical Considerations for Working With Low-Frequency Oscillators

- AN3208: Crystal Oscillator Troubleshooting Guide

Clocking

# Chapter 5 Power Management Control (PMC/SMC/LLWU/RCM)

#### 5.1 Introduction

This chapter is a brief description of the power management features of the Kinetis L series 32-bit MCU.

There are four modules covered in this chapter:

- Power Management Controller (PMC)

- System Mode Controller (SMC)

- Low Leakage Wake-up Unit (LLWU)

- Reset Control Module(RCM)

# 5.2 Using the power management controller

## 5.2.1 Overview

This section will demonstrate how to use the power management controller (PMC) to protect an MCU from unexpected low  $V_{DD}$  events. References to other protection options will also be made.

# 5.2.2 Using the low voltage detection system

#### 5.2.2.1 POR and LVD features

The POR and LVD functions allow protection of memory contents from brown out conditions and the operation of the MCU below the specified VDD levels. As noted in the module operation in the low power modes section, the LVD circuit is available only

#### Using the low voltage detection system

in RUN, WAIT, and STOP modes. POR circuitry is on in all modes and can be optionally disabled in VLLS0. The user has control over whether LVD is used and whether the POR is enabled in the lowest power mode (VLLS0). When using the low voltage detect features, the user has full control over the LVD and LVW trip voltages. The LVW is a warning detect circuit and the LVD is reset detect circuit.

As voltage falls below the warning level, the LVW circuit flags the warning event and can cause an interrupt. If the voltage continues to fall, the LVD circuit flags the detect event and can either cause a reset or an interrupt. The user can choose what action to take in the interrupt service routine. If a detect is selected to drive reset, the LVD circuit holds the MCU in reset until the supply voltage rises above the detect threshold.

The POR circuit for the MCU will hold the MCU in reset based upon the VDD voltage. Before entering the VLLS0 low power mode, the user can choose to disable the POR circuit. Because the MCU is switched off in VLLS0, the POR protection is not really needed and can be disabled. This saves a few hundred nano amps of power while the MCU is in this mode.

If the POR circuit is disabled in VLLS0, the MCU will continue to hold the state of the pins until the VDD levels are much lower than the POR trip voltage levels.

Exiting VLLS0 follows the reset mode. The POR circuit is reenabled protecting the MCU operation during the recovery.

# 5.2.2.2 Configuration examples

LVD and LVW initialization code is given below: Notice the comments describing the chosen settings. You should select the parameter options for your application. The NVIC vector flag may be set and is cleared if interrupts are enabled. The Interrupt is enabled in the NVIC in this initialization with the call to function enable\_irq(LVD\_irq\_no):

```

/* LVD and LVD initialzation routine.

* sets up the LVD and LVW control registers

* This function can be used to set up the low voltage detect

* and warning. While the device is in the very low power or low

* leakage modes, the LVD system is disabled regardless of LVDSC1

* settings. To protect systems that must have LVD always on,

* configure the SMC's power mode protection register (PMPROT)

* to disallow any very low power or low leakage modes from

* being enabled.

* Parameters:

lvd select = 0x00 Low trip point selected (V LVD = V LVDL )

= 0x01 High trip point selected (V LVD = V LVDH )

= 0x10 Reserved

= 0x11 Reserved

* lvd reset enable = 0x00 LVDF does not generate hardware resets

= 0x10 Force an MCU reset when LVDF = 1

* lvd_int_enable = 0x00 Hardware interrupt disabled

```

```

= 0x20 Request a hardware interrupt if LVDF = 1

lvw select = 0x00 Low trip point selected (VLVW = VLVW1)

= 0x01 Mid 1 trip point selected (VLVW = VLVW2)

= 0x10 Mid 2 trip point selected (VLVW = VLVW3)

= 0x11 High trip point selected (VLVW = VLVW4)

* lvw int enable = 0x00 Hardware interrupt disabled

= 0x20 Request a hardware interrupt if LVWF = 1

void LVD Initalize (unsigned char lvd select,

unsigned char lvd reset enable,

unsigned char lvd int_enable,

unsigned char lvw select,

unsigned char lvw int enable) {

/*enable LVD Reset ? LVD Interrupt.select high or low LVD */

PMC LVDSC1 = PMC LVDSC1 LVDACK MASK

(lvd reset enable)

lvd int enable

PMC LVDSC1 LVDV(lvd select);

/* select LVW level 1,2,\frac{1}{3} or 4 */

PMC LVDSC2 = PMC LVDSC2 LVWACK MASK

(lvw_int_enable) | //LVW i:

PMC_LVDSC2_LVWV(lvw_select);

//LVW interrupt?

/* if interrupts requested

clear pending flags in NVIC and enable interrupts */

if (((PMC LVDSC1 & PMC LVDSC1 LVDIE MASK)

>>PMC LVDSC1 LVDIE SHIFT)

((PMC LVDSC2 & PMC LVDSC2 LVWIE MASK)

>>PMC LVDSC2 LVWIE SHIFT))

enable irq(LVD irq no); // ready for this interrupt.

}

```

## 5.2.2.3 Interrupt code example and explanation

The LVD circuitry can be programmed to cause an interrupt. You should create a service routine to clear the flags and react appropriately. An example of such an interrupt service routine is given.

To clear a warning or detect interrupt flag two things must happen:

- 1. The VDD voltage must return to a nominal voltage above the threshold.

- 2. A write to the LVDACK bit must be done to clear the LVDF indicator or a write to the LVWACK bit must be done to clear the LVWF indicator.

If the ACK bit is written and the voltage does not go back above the threshold, the interrupt flag will not clear and the interrupt routine will be reentered.

```

void pmc_lvd_isr(void)

{

if (PMC_LVDSC1 &PMC_LVDSC1_LVDF_MASK) {

printf("[LVD_isr]LV DETECT interrupt occurred");

}

if (PMC_LVDSC2 &PMC_LVDSC2_LVWF_MASK) {

printf("[LVD_isr]LV WARNING interrupt occurred");

}

}

```

#### Using the low voltage detection system

```

// ack to clear initial flags

PMC_LVDSC1 |= PMC_LVDSC1_LVDACK_MASK;

PMC_LVDSC2 |= PMC_LVDSC2_LVWACK_MASK;

}

```

#### 5.2.2.4 Hardware implementation

**RESET PIN:** The reset pin is an open drain and has an internal pullup device. The pin is driven out if the internal circuitry detects a reset. This is true for all resets, except when there is a recovery from the VLLSx modes.

Although the wake-up recovery from VLLSx modes is through the reset flow, the reset pin is not driven out of the MCU. The reason for this is that I/O is held in the pre-low-power mode entry state so the internal reset action is blocked from being driven out.

If reset is driven low for longer than minimum pulse width to pass the analog filter and the digital filter settings, the MCU will wake from any low-power mode and the PIN bit in the RCM\_SRS0 register will be set.

The reset pin can be disabled by clearing the RESET\_PIN\_CFG bit in the Flash Option Register (FOPT).

**VDD:** The VDD supply pins can be driven between 1.71 V and 3.6 V DC.

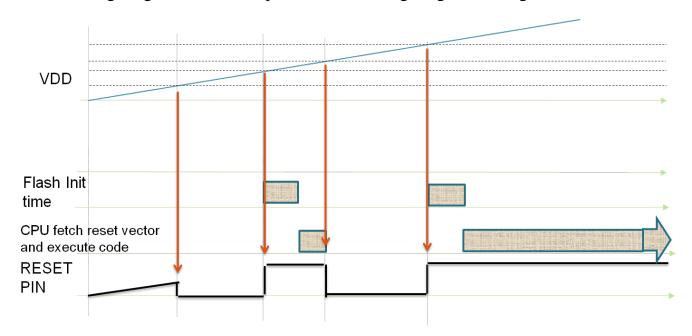

The following diagram shows a representative timing diagram during POR.

Figure 5-1. Representative timing diagram during POR

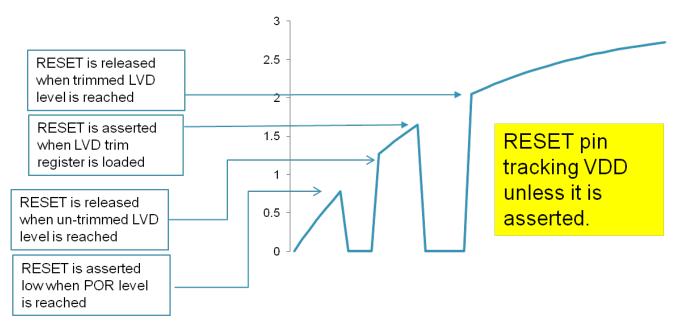

The following diagram shows the observed behavior of the reset pin during a ramp of VDD. In both of the following diagrams RESET asserts initially as the POR circuit is powered up. Next RESET is released when untrimmed LVD level is reached. Next RESET is asserted when LVD trim register is loaded, followed by RESET being released when trimmed LVD level is reached.

Figure 5-2. Observed RESET pin behavior during normal slow VDD rise

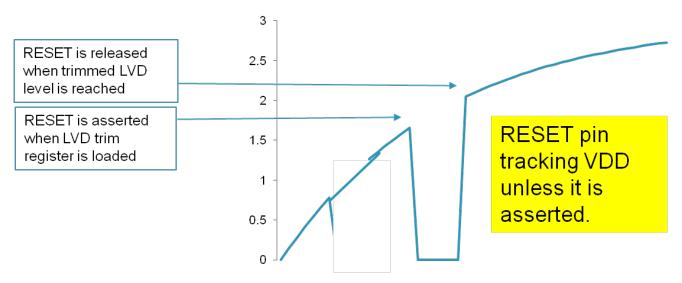

The following diagram shows the observed behavior of the reset pin during a fast ramp of VDD.

Figure 5-3. Observed RESET pin behavior during normal fast VDD rise

# 5.3 Using the system mode controller

#### 5.3.1 Overview

This section will demonstrate how to use the system mode controller (SMC). The SMC is responsible for controlling the entry and exit from all of the run, wait, and stop modes of the MCU. This module works in conjunction with the RCM, PMC, and the LLWU to wake-up the MCU and move between power modes.

#### 5.3.1.1 Introduction

There are 10 power modes and some new clocking options. These modes and options are described below.

- 1. Run Default Operation of the MCU out of Reset, On-chip voltage regulator is On, full capability.

- 2. Very Low Power Run (VLPR) On-chip voltage regulator is in a mode that supplies only enough power to run the MCU in a reduced frequency. Core and Bus frequency limited to 2 MHz.

- 3. Wait ARM core enters Sleep mode, NVIC remains sensitive to interrupts, Peripherals Continue to be clocked.

- 4. Stop ARM core enters DeepSleep mode, NVIC is disabled, WIC is used to wake up from interrupt, peripheral clocks are stopped.

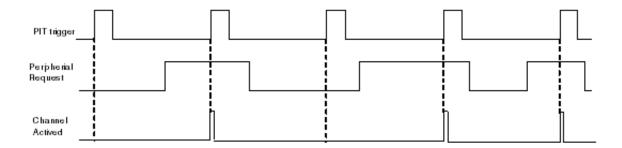

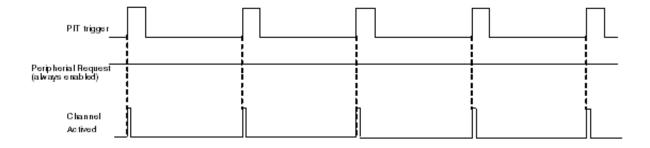

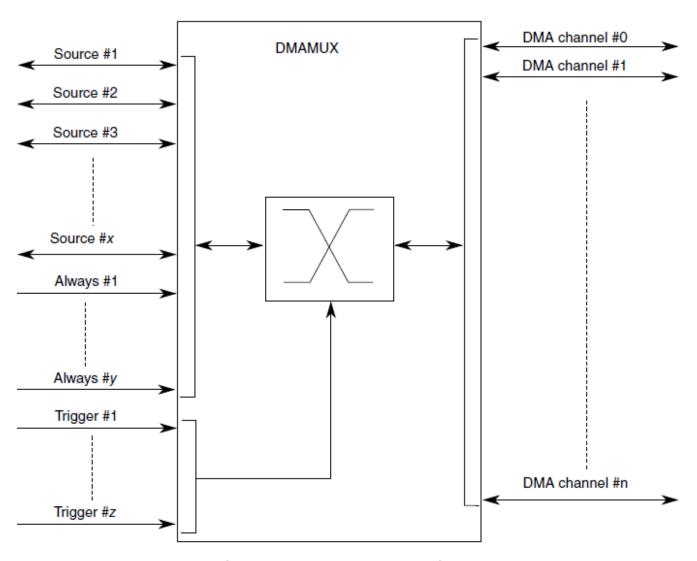

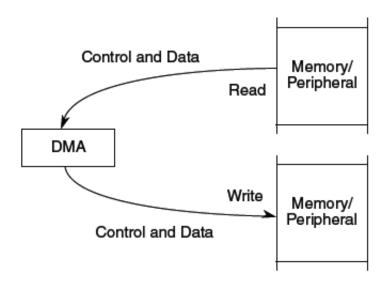

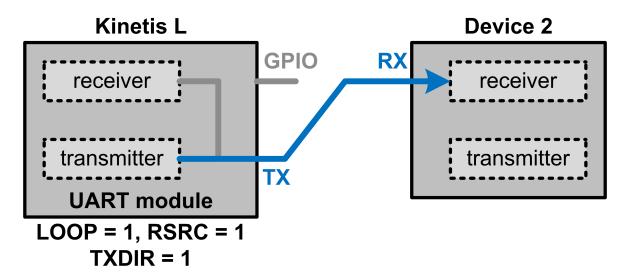

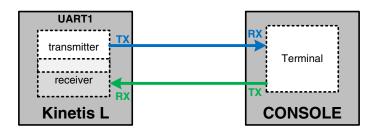

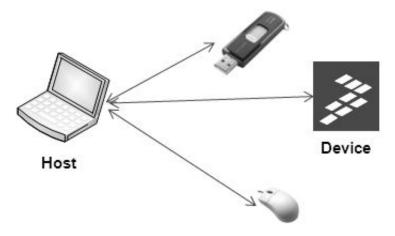

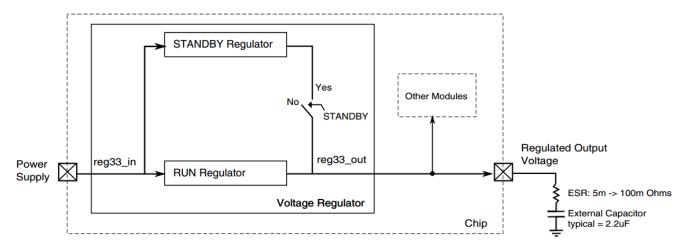

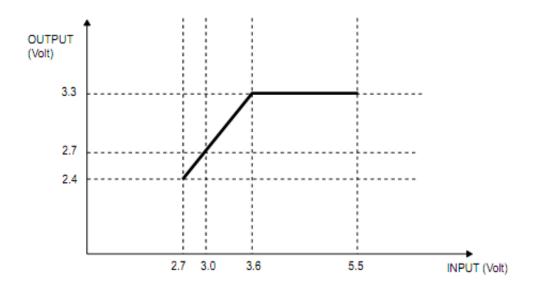

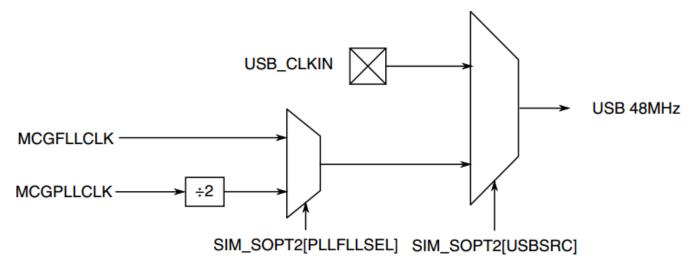

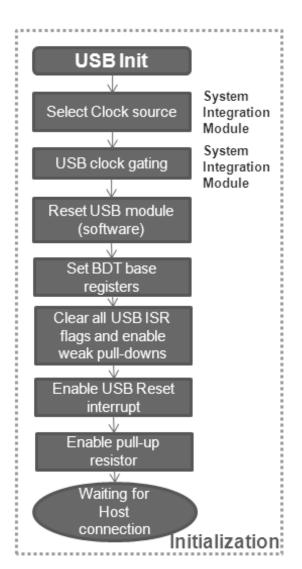

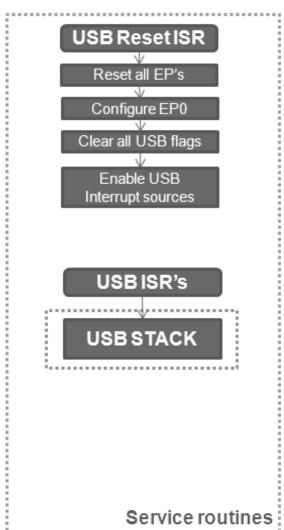

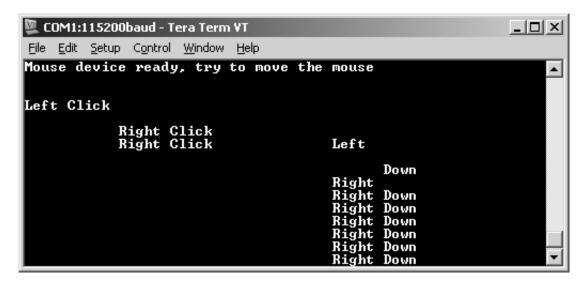

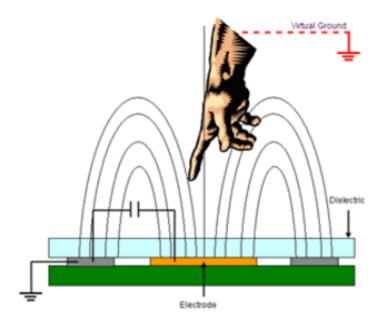

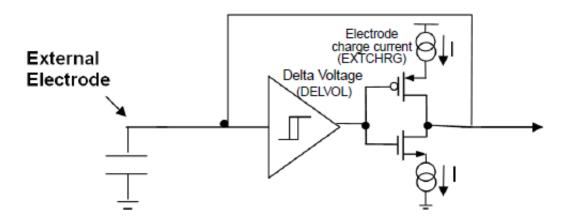

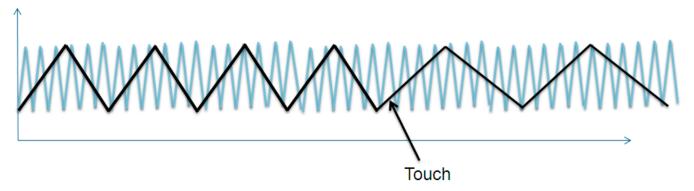

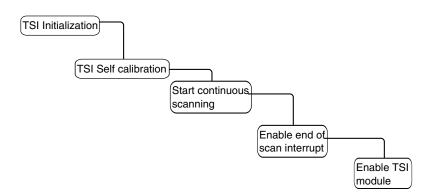

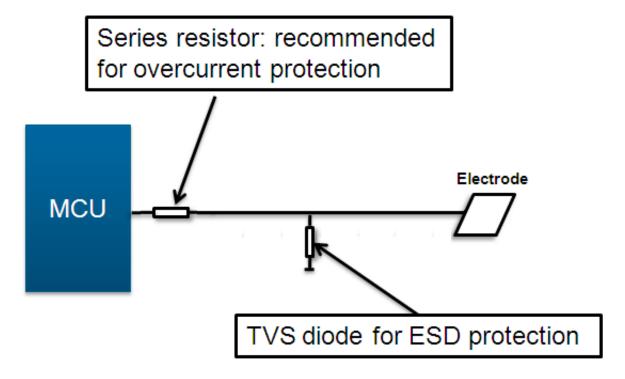

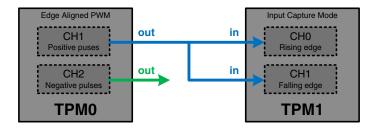

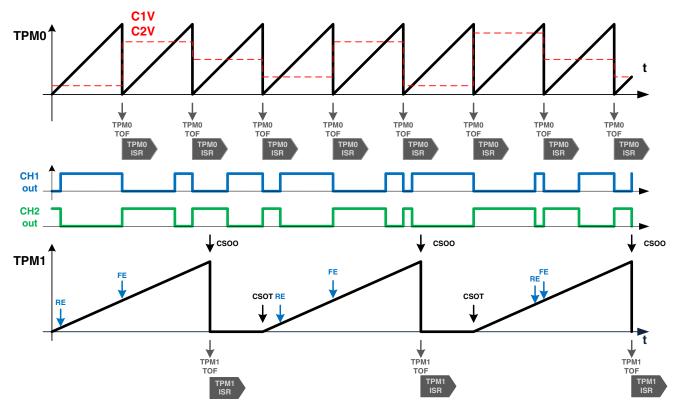

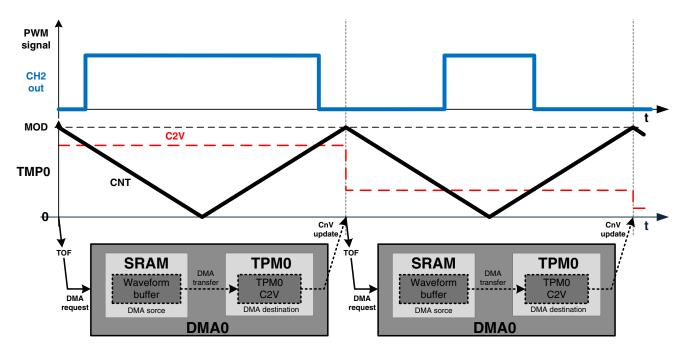

- 5. Very Low Power Wait (VLPW) ARM core enters Sleep mode, NVIC remains sensitive to interrupts (FCLK = ON), On-chip voltage regulator is in a mode that supplies only enough power to run the MCU at a reduced frequency.