# **EA075**Processadores Dedicados

Faculdade de Engenharia Elétrica e de Computação (FEEC) Universidade Estadual de Campinas (UNICAMP)

Prof. Rafael Ferrari

(Documento baseado nas notas de aula do Prof. Levy Boccato)

# Introdução

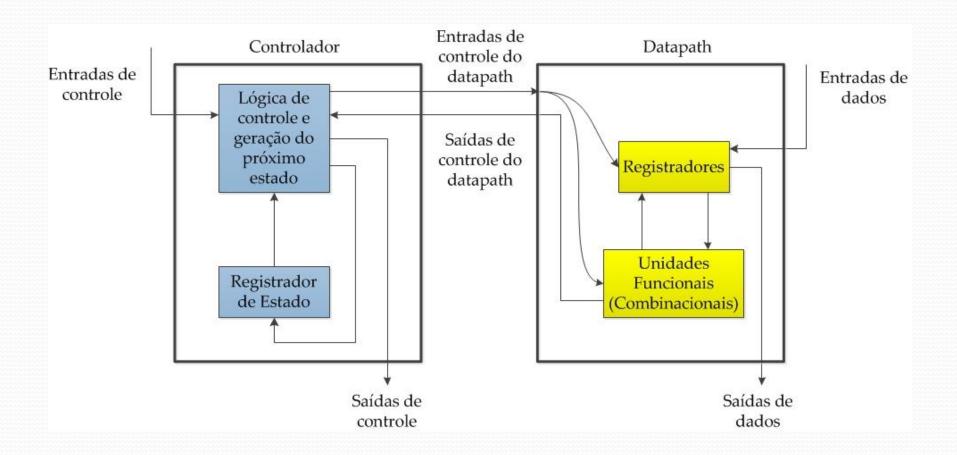

• **Processador:** circuito digital projetado para realizar tarefas de computação.

#### Dois elementos básicos:

- > Datapath: responsável por armazenar e manipular dados.

- > Controlador (Unidade de controle): responsável por gerenciar a execução ordenada das operações.

# Introdução

- **Processador Dedicado:** é construído para realizar uma tarefa de computação específica.

- Algumas tarefas são tão comuns que é possível encontrar processadores dedicados padronizados que as implementam (e.g., temporizadores, ADCs, etc.)

- Outras, porém, são particulares para um determinado sistema embarcado.

- Nestes casos, a ideia de projetar o processador surge como uma opção interessante.

# Introdução

## Motivação

- A opção por efetivamente projetar o processador pode trazer alguns benefícios:

- > Melhor desempenho: mais rápidos

- > Menor ocupação de área no circuito integrado

- Menor consumo de potência

### • Trade-offs:

- > Alto custo de projeto do modelo completo do sistema (custo NRE).

- > Tempo para lançamento do dispositivo no mercado será maior.

- > Baixa flexibilidade.

- > Custo por unidade pode ser elevado para produção em baixa escala.

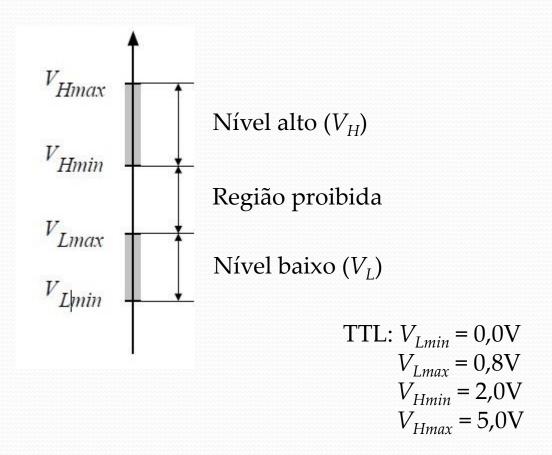

• Sistemas digitais: são sistemas nos quais os sinais podem assumir um conjunto finito de valores discretos.

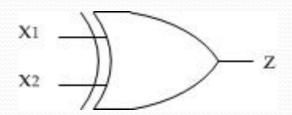

#### Sistemas combinacionais

- Em qualquer instante, o nível lógico na saída do sistema corresponde a uma combinação dos níveis lógicos presentes nas entradas (i.e., depende apenas dos valores atuais das entradas).

- Função de saída: z(t) = F(x(t))

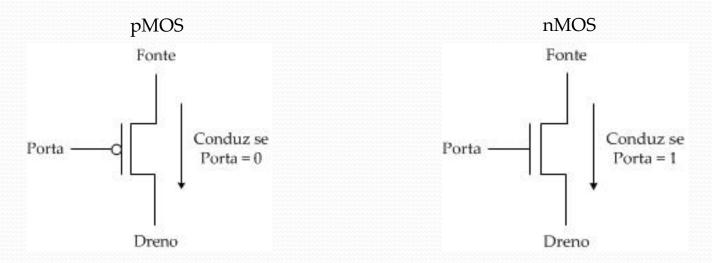

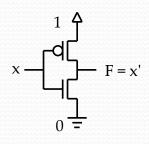

- Elemento básico: transistor.

- Atua como uma chave liga/desliga.

- ➤ A tensão colocada na porta (gate) determina o fluxo de corrente entre a fonte e o dreno.

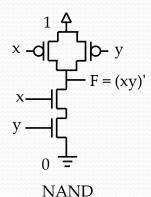

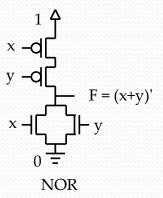

- > CMOS (complementary metal oxide semiconductor):

É possível construir funções lógicas usando transistores pMOS e nMOS.

- pMOS: conduzem bem tensões altas (nível 1).

- nMOS: conduzem bem tensões baixas (nível 0).

- ➤ Por isso, transistores nMOS são usados na parte do circuito associada ao conjuntozero de uma função lógica, enquanto transistores pMOS são utilizados no circuito referente ao conjunto-um.

- Exemplos: inversor (NOT), NAND e NOR

inversor

| X | V | F |

|---|---|---|

| 0 | Ó | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| X                      | V | F |

|------------------------|---|---|

| $\frac{\mathbf{x}}{0}$ | Ó | 1 |

| 0                      |   | 0 |

| 1                      | 0 | 0 |

| 1                      | 1 | 0 |

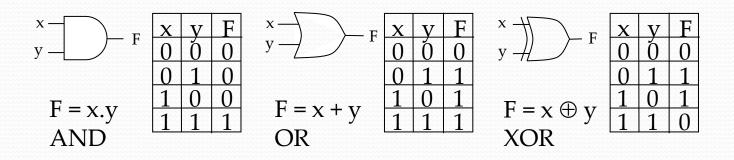

• É preferível trabalhar no nível de abstração de portas lógicas.

### Projeto de Lógica Combinacional

### Exemplo

#### 1. Descrição do problema

Como as variáveis de saída se comportam em função das variáveis de entrada.

#### 2. Tabela verdade

| Е | Entradas |   |   | das |

|---|----------|---|---|-----|

| x | y        | Z | r | s   |

| 0 | 0        | 0 | 0 | 1   |

| 0 | 0        | 1 | 0 | 1   |

| 0 | 1        | 0 | 1 | 0   |

| 0 | 1        | 1 | 1 | 0   |

| 1 | 0        | 0 | 0 | 1   |

| 1 | 0        | 1 | 0 | 1   |

| 1 | 1        | 0 | 0 | 0   |

| 1 | 1        | 1 | 1 | 0   |

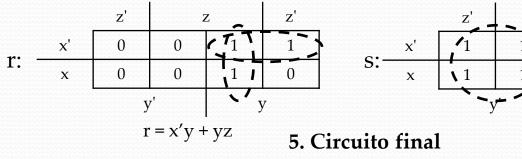

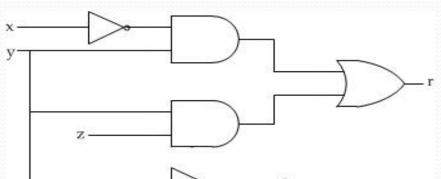

#### 3. Expressões booleanas

$$r = x'yz' + x'yz + xyz$$

$$s = x'y'z' + x'y'z + xy'z' + xy'z$$

#### 4. Minimização das equações de saídas

z'

0

0

s = v'

# Componentes Combinacionais

| I(m-1) I1 I0  n So n-bit, m x 1  Multiplexador  S(log m) O | I(log n -1)I0 log n x n Decoder O(n-1) O1O0                             | A B n-bit Somador n carry soma                                                 | A B n n-bit Comparador menor igual maior                             | A B n n bit, m funções ULA  N S(log m) O               |

|------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------|

| O = I0 se S=000 I1 se S=001 I(m-1) se S=111                | O0 =1 se I=000<br>O1 =1 se I=001<br><br>O(n-1) =1 se I=111              | soma = A+B<br>(primeiros n bits)<br>carry (vai um) =<br>(n+1)'ésimo bit de A+B | menor = 1 se A <b<br>igual = 1 se A=B<br/>maior = 1 se A&gt;B</b<br> | O = A op B<br>op determinado por S.                    |

|                                                            | Com entrada de<br>habilitação (enable) e<br>→ todos O's são 0 se<br>e=0 | Com entrada de<br>carry-in Ci→<br>soma = A + B + Ci                            |                                                                      | Pode possuir saídas<br>de status, carry, zero,<br>etc. |

# Multiplexadores

- Seleciona e conecta uma de suas *n* entradas à saída.

- A escolha é feita através de  $log_2(n)$  entradas de seleção.

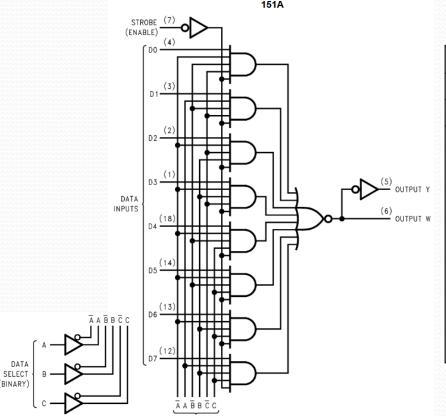

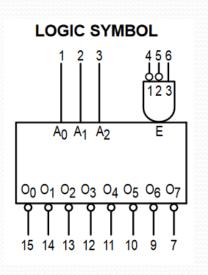

- Exemplo: 74151 1bit,  $8 \times 1$  multiplexer

|   | li     | Out | puts   |    |                |

|---|--------|-----|--------|----|----------------|

|   | Select |     | Strobe | Y  | W              |

| С | В      | Α   | S      |    |                |

| Х | Х      | Х   | Н      | L  | Н              |

| L | L      | L   | L      | D0 | D0             |

| L | L      | Н   | L      | D1 | D1             |

| L | Н      | L   | L      | D2 | D2             |

| L | Н      | Н   | L      | D3 | D3             |

| Н | L      | L   | L      | D4 | <del>D</del> 4 |

| Н | L      | Н   | L      | D5 | D5             |

| Н | Н      | L   | L      | D6 | <del>D</del> 6 |

| Н | Н      | Н   | L      | D7 | D7             |

### Decodificadores

- Ativa uma de suas n saídas de acordo com o valor em suas  $\log_2(n)$  entradas  $\rightarrow \log_2(n) \times n$  decoder.

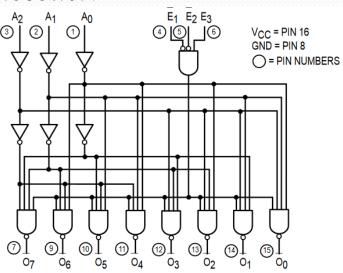

- Exemplo:  $74138 3 \times 8$  decoder

| 88 | INPUTS         |                |                |                |                |                |    |    | OU. | TPUTS |    |    |    |                     |

|----|----------------|----------------|----------------|----------------|----------------|----------------|----|----|-----|-------|----|----|----|---------------------|

| 8  | E <sub>1</sub> | E <sub>2</sub> | E <sub>3</sub> | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | 00 | 01 | 02  | 03    | 04 | 05 | 06 | _<br>0 <sub>7</sub> |

| 8  | Н              | X              | X              | X              | X              | X              | Н  | Н  | Н   | Н     | Н  | Н  | Н  | Н                   |

| 8  | X              | Н              | X              | X              | X              | X              | Н  | Н  | Н   | Н     | Н  | Н  | Н  | Н                   |

| 8  | X              | X              | L              | X              | X              | X              | Н  | Н  | Н   | Н     | Н  | Н  | Н  | Н                   |

| 8  | L              | L              | Н              | L              | L              | L              | L  | Н  | Н   | Н     | Н  | Н  | Н  | Н                   |

| 8  | L              | L              | Н              | Н              | L              | L              | Н  | L  | Н   | Н     | Н  | Н  | Н  | Н                   |

| 8  | L              | L              | Н              | L              | Н              | L              | Н  | Н  | L   | Н     | Н  | Н  | Н  | Н                   |

| 8  | L              | L              | Н              | Н              | Н              | L              | Н  | Н  | Н   | L     | Н  | Н  | Н  | Н                   |

| 8  | L              | L              | Н              | L              | L              | Н              | Н  | Н  | Н   | Н     | L  | Н  | Н  | Н                   |

| 8  | L              | L              | Н              | Н              | L              | Н              | Н  | Н  | Н   | Н     | Н  | L  | Н  | Н                   |

| 8  | L              | L              | Н              | L              | Н              | Н              | Н  | Н  | Н   | Н     | Н  | Н  | L  | Н                   |

| 8  | L              | L              | Н              | Н              | Н              | Н              | Н  | Н  | Н   | Н     | Н  | Н  | Н  | L                   |

### Somadores

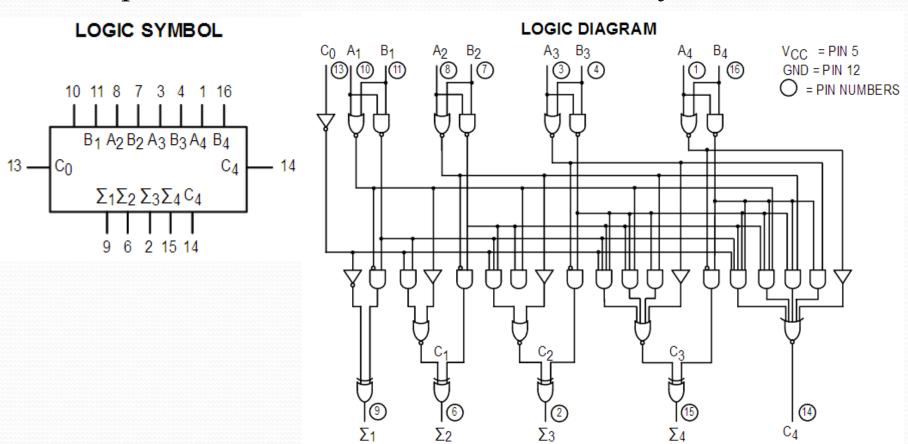

• Exemplo: 7483 – somador de 4 bits com *carry*

$C_0 + (A_1+B_1)+2(A_2+B_2)+4(A_3+B_3)+8(A_4+B_4) = \sum_{1}+2\sum_{2}+4\sum_{3}+8\sum_{4}+16C_4$

### Comparadores

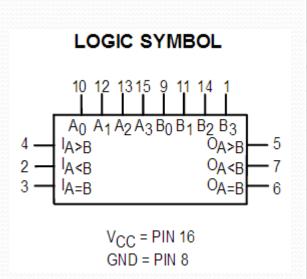

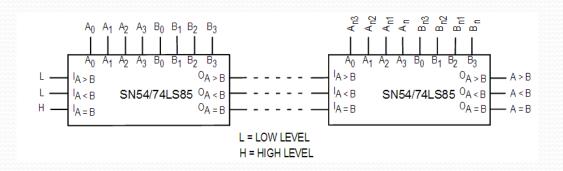

• Exemplo: 7485 – comparador de 4 bits

| COMPARING INPUTS                                                                                               |                                 |                                                                                            | CASCADING<br>INPUTS             |                     |                                | OUTPUTS          |                     |                                |                  |

|----------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------|---------------------------------|---------------------|--------------------------------|------------------|---------------------|--------------------------------|------------------|

| A <sub>3</sub> ,B <sub>3</sub>                                                                                 | A2,B2                           | A <sub>1</sub> ,B <sub>1</sub>                                                             | $A_0,B_0$                       | I <sub>A&gt;B</sub> | I <sub>A<b< sub=""></b<></sub> | I <sub>A=B</sub> | O <sub>A&gt;B</sub> | O <sub>A<b< sub=""></b<></sub> | O <sub>A=B</sub> |

| A3>B3                                                                                                          | X                               | Х                                                                                          | X                               | Х                   | X                              | X                | Н                   | L                              | L                |

| A3 <b3< td=""><td>X</td><td>X</td><td>X</td><td>Х</td><td>X</td><td>X</td><td>L</td><td>Н</td><td>L</td></b3<> | X                               | X                                                                                          | X                               | Х                   | X                              | X                | L                   | Н                              | L                |

| A3=B3                                                                                                          | A2>B2                           | X                                                                                          | X                               | Х                   | X                              | X                | Н                   | L                              | L                |

| A3=B3                                                                                                          | A <sub>2</sub> <b<sub>2</b<sub> | X                                                                                          | X                               | X                   | X                              | X                | L                   | Н                              | L                |

| A3=B3                                                                                                          | $A_2 = B_2$                     | A <sub>1</sub> >B <sub>1</sub>                                                             | X                               | X                   | X                              | X                | Н                   | L                              | L                |

| A3=B3                                                                                                          | A2=B2                           | A1 <b1< td=""><td>X</td><td>X</td><td>X</td><td>X</td><td>L</td><td>Н</td><td>L</td></b1<> | X                               | X                   | X                              | X                | L                   | Н                              | L                |

| A3=B3                                                                                                          | $A_2 = B_2$                     | A <sub>1</sub> =B1                                                                         | A <sub>0</sub> >B <sub>0</sub>  | X                   | X                              | X                | Н                   | L                              | L                |

| A3=B3                                                                                                          | $A_2 = B_2$                     | A <sub>1</sub> =B <sub>1</sub>                                                             | A <sub>0</sub> <b<sub>0</b<sub> | X                   | X                              | X                | L                   | Н                              | L                |

| A3=B3                                                                                                          | A2=B2                           | A1=B1                                                                                      | A <sub>0</sub> =B <sub>0</sub>  | Н                   | L                              | L                | Н                   | L                              | L                |

| A3=B3                                                                                                          | A2=B2                           | A <sub>1</sub> =B <sub>1</sub>                                                             | $A_0 = B_0$                     | L                   | Н                              | L                | L                   | Н                              | L                |

| A3=B3                                                                                                          | A2=B2                           | A <sub>1</sub> =B <sub>1</sub>                                                             | $A_0 = B_0$                     | X                   | X                              | Н                | L                   | L                              | Н                |

| A3=B3                                                                                                          | A2=B2                           | A <sub>1</sub> =B <sub>1</sub>                                                             | A <sub>0</sub> =B <sub>0</sub>  | Н                   | Н                              | L                | L                   | L                              | L                |

| A3=B3                                                                                                          | A <sub>2</sub> =B <sub>2</sub>  | A <sub>1</sub> =B <sub>1</sub>                                                             | A <sub>0</sub> =B <sub>0</sub>  | L                   | L                              | L                | Н                   | H                              | L                |

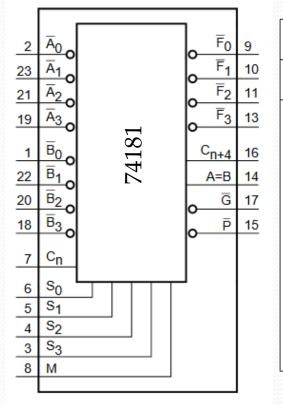

### Unidades lógico-aritméticas (ULA)

- Permite a execução de diversas operações lógicas e aritméticas em seus operandos de entrada.

- Exemplo: 74181 4-bit ULA

| MODE SELECT<br>INPUTS |                |                | СТ             | ACTIVE HIGH INPUTS AND OUTPUTS |                                                    |  |

|-----------------------|----------------|----------------|----------------|--------------------------------|----------------------------------------------------|--|

| S <sub>3</sub>        | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | LOGIC<br>(M=H)                 | ARITHMETIC <sup>(2)</sup> (M=L; C <sub>n</sub> =H) |  |

| L                     | L              | L              | L              | Ā                              | Α                                                  |  |

| L                     | L              | L              | Н              | A + B                          | A + B                                              |  |

| L                     | L              | Н              | L              | ĀB                             | A + B                                              |  |

| L                     | L              | Н              | Н              | logical 0                      | minus 1                                            |  |

| L                     | Н              | L              | L              | ĀB                             | A plus AB                                          |  |

| L                     | Н              | L              | Н              | B                              | (A + B) plus AB                                    |  |

| L<br>L                | Н              | Н              | L              | A⊕B                            | A minus B minus 1                                  |  |

| L                     | Н              | Н              | Н              | AB                             | AB minus 1                                         |  |

| Н                     | L              | L              | L              | Ā + B                          | A plus AB                                          |  |

| Н                     | L              | L              | Н              | Ā⊕B                            | A plus B                                           |  |

| Н                     | L              | Н              | L              | В                              | (A + B) plus AB                                    |  |

| Н                     | L              | Н              | Н              | AB                             | AB minus 1                                         |  |

| Н                     | Н              | L              | L              | logical 1                      | A plus A <sup>(1)</sup>                            |  |

| Н                     | Н              | L              | Н              | A + B                          | (A + B) plus A                                     |  |

| Н                     | Н              | Н              | L              | A + B                          | (A + B) plus A                                     |  |

| Н                     | Н              | Н              | Н              | Α                              | A minus 1                                          |  |

| M              | MODE SELECT<br>INPUTS |                |                | ACTIVE LOW INPUTS AND OUTPUTS |                                                       |

|----------------|-----------------------|----------------|----------------|-------------------------------|-------------------------------------------------------|

| S <sub>3</sub> | S <sub>2</sub>        | S <sub>1</sub> | S <sub>0</sub> | LOGIC<br>(M=H)                | ARITHMETIC <sup>(2)</sup><br>(M=L; C <sub>n</sub> =L) |

| L              | L                     | L              | L              | Ā                             | A minus 1                                             |

| L              | L                     | L              | Н              | AB                            | AB minus 1                                            |

| L              | L                     | Н              | L              | Ā + B                         | AB minus 1                                            |

| L              | L                     | Н              | Н              | logical 1                     | minus 1                                               |

| L              | Н                     | L              | L              | A + B                         | A plus (A + B)                                        |

| L              | Н                     | L              | Н              | B                             | AB plus (A + $\overline{B}$ )                         |

| L              | Н                     | Н              | L              | Ā⊕B                           | A minus B minus 1                                     |

| L              | Н                     | Н              | Н              | A + B                         | A + B                                                 |

| Н              | L                     | L              | L              | ĀB                            | A plus (A + B)                                        |

| Н              | L                     | L              | Н              | A⊕B                           | A plus B                                              |

| Н              | L                     | Н              | L              | В                             | $A\overline{B}$ plus (A + B)                          |

| Н              | L                     | Н              | Н              | A + B                         | A + B                                                 |

| Н              | Н                     | L              | L              | logical 0                     | A plus A <sup>(1)</sup>                               |

| Н              | Н                     | L              | Н              | AB                            | AB plus A                                             |

| Н              | Н                     | Н              | L              | AB                            | AB plus A                                             |

| Н              | Н                     | Η              | Н              | Α                             | Α                                                     |

### Buffer tri-state

- Opera de modo equivalente a uma chave.

- Pode ser usado para viabilizar a conexão de várias saídas a uma mesma entrada.

- Pode ser usado para aumentar a corrente máxima fornecida por uma saída (driver).

| В | A | С               |

|---|---|-----------------|

| 0 | X | Alta impedância |

| 1 | 0 | 0               |

| 1 | 1 | 1               |

$$\stackrel{\mathsf{B}}{\longrightarrow} \qquad \stackrel{\mathsf{C}}{=} \qquad \stackrel{\mathsf{B}}{\longrightarrow} \qquad \stackrel{\mathsf{C}}{\longrightarrow} \qquad \stackrel{\mathsf$$

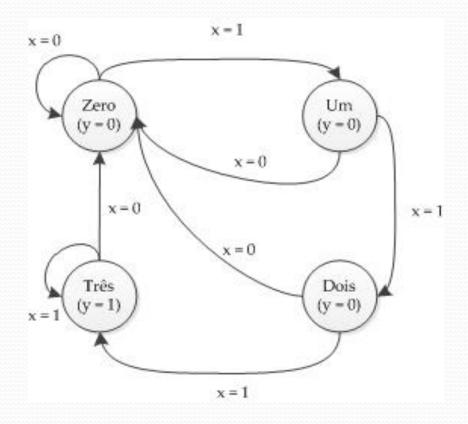

### • Sistemas sequenciais

- Em qualquer instante de tempo *t*, a saída é uma função dos níveis lógicos das entradas atuais, bem como de seus valores em instantes anteriores.

- ➤ A dependência temporal do sistema é modelada por meio de uma máquina de estados finitos, de modo que o comportamento do sistema sequencial passa a ser descrito por meio das seguintes funções:

- > Função de transição de estado: s(t+1) = G(x(t),s(t))

- > Função de saída: z(t) = H(s(t), x(t))

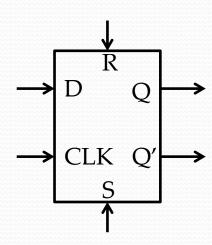

# Flip Flop

• Elemento de memória: circuito combinacional com realimentação.

• Flip Flop D:

| R | S | CLK        | D | Q  |

|---|---|------------|---|----|

| 0 | 0 | $\uparrow$ | 0 | 0  |

| 0 | 0 | $\uparrow$ | 1 | 1  |

| 0 | 0 | not rising | X | Qa |

| 1 | 0 | Χ          | X | 0  |

| 0 | 1 | X          | X | 1  |

# Projeto de Lógica Sequencial

• Projeto via máquina de estados finitos

• Ex.: Detector de sequência '111'

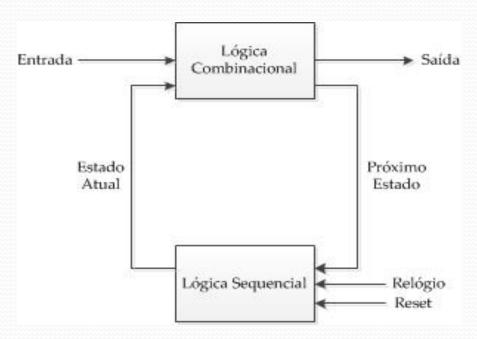

# Projeto de Lógica Sequencial

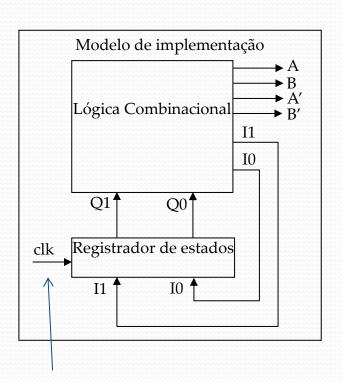

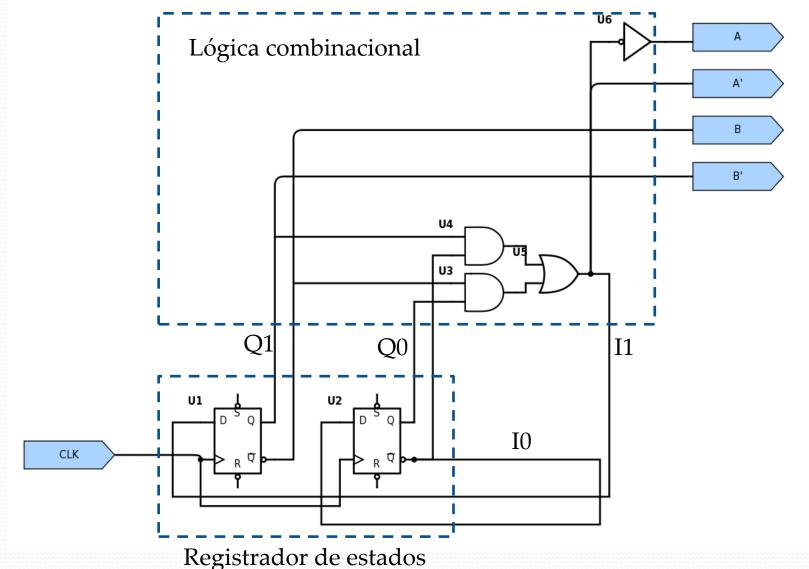

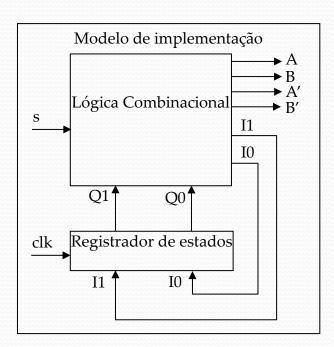

### • Forma canônica

- > Flip-flops / Registrador de estado: armazena o estado atual.

- > Circuito combinacional determina o próximo estado e as saídas.

# Projeto de Lógica Sequencial

### Etapas do projeto

- > Descrição do problema (variáveis de entrada e saída);

- > Elaboração de um diagrama de estados que representa o sistema;

- Definição de um modelo de implementação baseado na forma canônica;

- Criação de uma tabela verdade que relaciona o estado atual e as entradas com as saídas e o próximo estado;

- ➤ A partir desse ponto, o processo se resume ao projeto da lógica combinacional que produzirá a(s) saída(s) e o próximo estado.

- > Exemplo: projeto de um controlador de motor de passo

- É um motor de corrente contínua (CC) sem escovas que movimenta seu rotor em passos discretos.

- Pode ser precisamente posicionado em malha aberta, ou seja, não requer controle com realimentação.

- Muito usado em sistemas de posicionamento: leitores de CD/DVD, scanners, impressoras, plotters, máquinas CNC, impressoras 3D, etc.

- Vídeo que ilustra seu funcionamento:

https://www.youtube.com/watch?v=TWMai3oirnM&s pfreload=10

- Modos de acionamento:

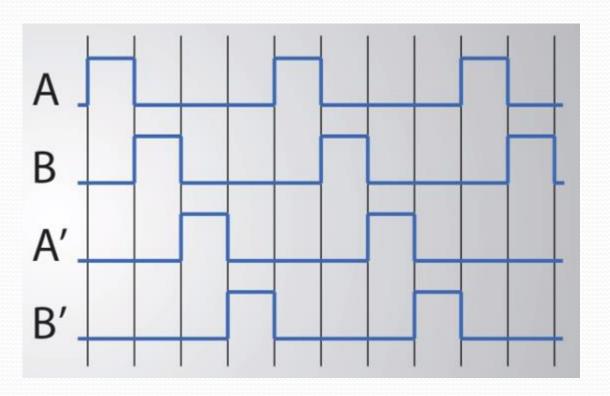

- ➤ Passo completo (*full step*) com uma única fase ativa por passo:

- Modos de acionamento:

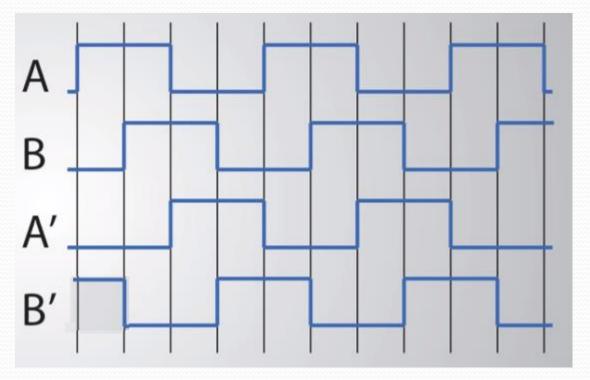

- ➤ Passo completo (*full step*) com duas fases ativas por passo:

➤ Maior torque.

- Modos de operação acionamento:

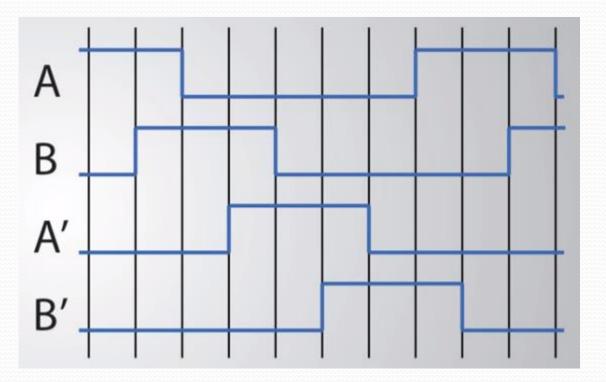

- ➤ Meio passo (*half step*) que combina o acionamento com uma e duas bobinas:

➤ Maior resolução.

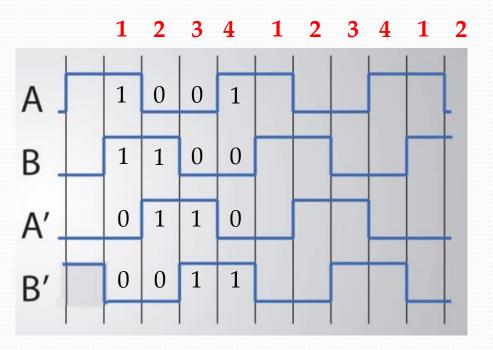

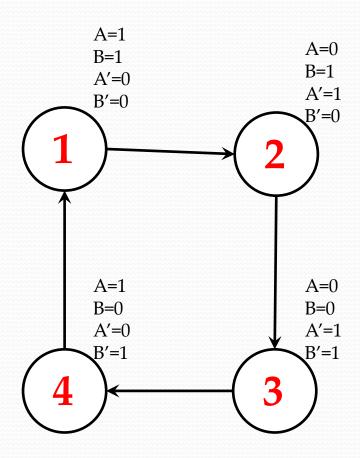

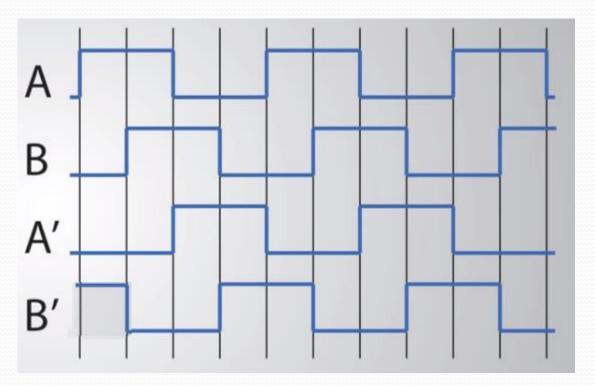

Projete um controlador que gere os sinais necessários para o acionamento de um motor de passo no modo passo completo com duas fases ativas por passo, de acordo com o diagrama de tempo abaixo.

| Estado | Q1 | Q0 |

|--------|----|----|

| 1      | 0  | 0  |

| 2      | 0  | 1  |

| 3      | 1  | 0  |

| 4      | 1  | 1  |

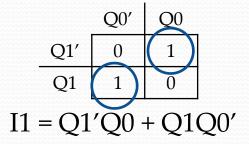

| Q1 | Q0 | I1 | I0 | A | В | A' | B' |

|----|----|----|----|---|---|----|----|

| 0  | 0  | 0  | 1  | 1 | 1 | 0  | 0  |

| 0  | 1  | 1  | 0  | 0 | 1 | 1  | 0  |

| 1  | 0  | 1  | 1  | 0 | 0 | 1  | 1  |

| 1  | 1  | 0  | 0  | 1 | 0 | 0  | 1  |

A cada borda de subida do relógio (clk) ocorre uma transição de estado que resulta em um passo do motor.

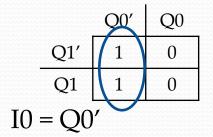

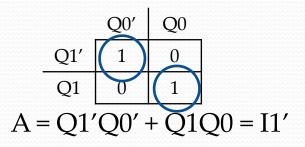

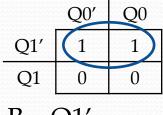

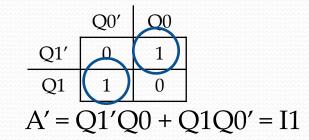

• Expressões simplificadas das saídas do circuito combinacional:

$$B = Q1'$$

- Um circuito digital geralmente não fornece a corrente (tensão) necessária para acionamento de um motor.

- É necessário usar algum tipo de amplificador (driver) analógico.

- No caso de motores de passo bipolares, é necessário empregar pontes H.

- Exemplo: L293D dupla ponte H de baixa potência (corrente máxima de 600mA)

- Livro interessante sobre o assunto (ebook disponível para download gratuito na rede da Unicamp):

- S. Ball, "Analog Interfacing to Embedded Microprocessor Systems", Elsevier, 2003.

https://www.elsevier.com/books/analog-interfacing-to-embedded-microprocessor-systems/ball/978-0-7506-7723-3

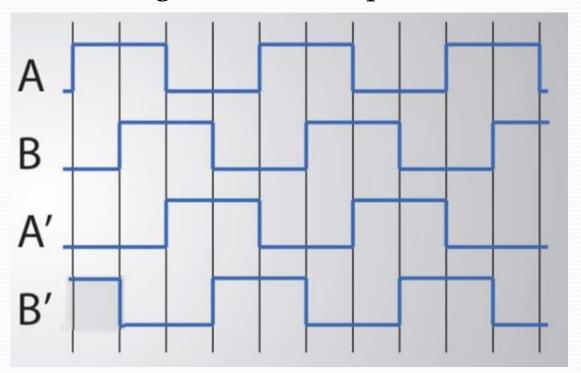

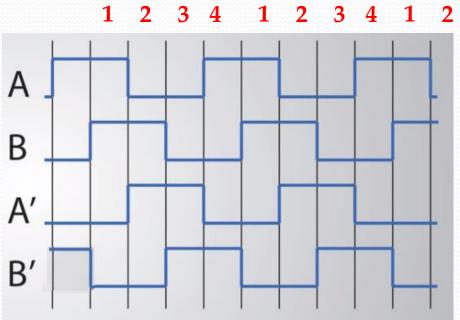

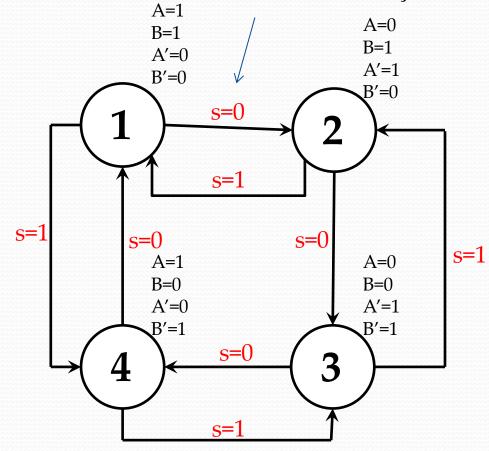

Projete um controlador que gere os sinais necessários para o acionamento de um motor de passo no modo passo completo com duas fases ativas por passo, de acordo com o diagrama de tempo abaixo. Acrescente um sinal que permita o controle do sentido de rotação do motor.

| Estado | Q1 | Q0 |

|--------|----|----|

| 1      | 0  | 0  |

| 2      | 0  | 1  |

| 3      | 1  | 0  |

| 4      | 1  | 1  |

**s**: entrada que controla o sentido de rotação

| S | Q1 | Q0 | I1 | IO | A | В | A' | B' |

|---|----|----|----|----|---|---|----|----|

| 0 | 0  | 0  | 0  | 1  | 1 | 1 | 0  | 0  |

| 0 | 0  | 1  | 1  | 0  | 0 | 1 | 1  | 0  |

| 0 | 1  | 0  | 1  | 1  | 0 | 0 | 1  | 1  |

| 0 | 1  | 1  | 0  | 0  | 1 | 0 | 0  | 1  |

| 1 | 0  | 0  | 1  | 1  | 1 | 1 | 0  | 0  |

| 1 | 0  | 1  | 0  | 0  | 0 | 1 | 1  | 0  |

| 1 | 1  | 0  | 0  | 1  | 0 | 0 | 1  | 1  |

| 1 | 1  | 1  | 1  | 0  | 1 | 0 | 0  | 1  |

# Controlador de motor de passo

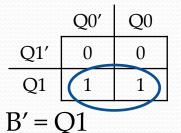

• Expressões simplificadas das saídas do circuito combinacional:

$$I1 = s'Q1'Q0' + s'Q1Q0' + sQ1'Q0' + sQ1Q0$$

$I0 = Q0'$

$A = Q1'Q0' + Q1Q0$

$B = Q1'$

$A' = Q1'Q0 + Q1Q0'$

$B' = Q1$

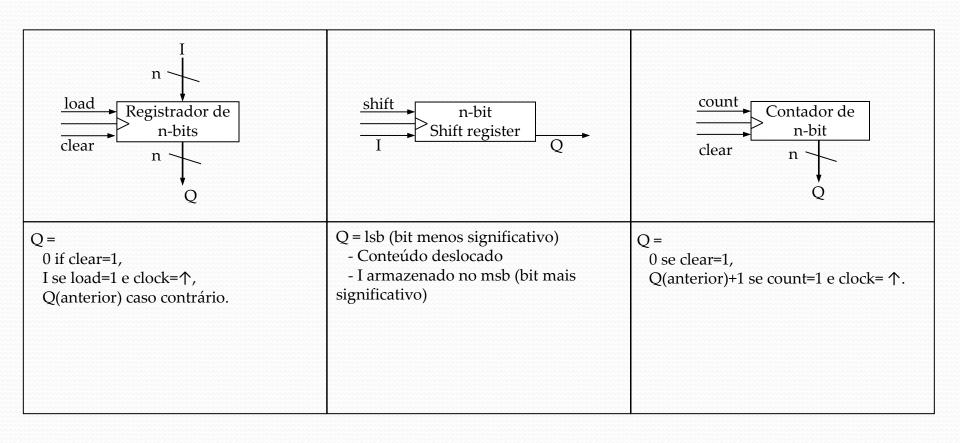

# Componentes Sequenciais

# Registradores

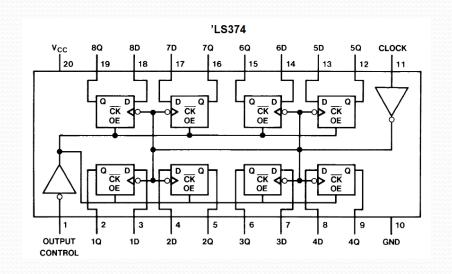

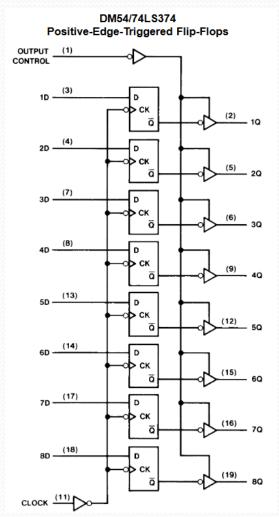

• Exemplo: 74374 – registrador de 8 bits

| Output<br>Control | Clock    | D | Output |

|-------------------|----------|---|--------|

| L                 | 1        | Н | Н      |

| L                 | <u> </u> | L | L      |

| L                 | L        | X | $Q_0$  |

| Н                 | X        | X | Z      |

# Registradores de deslocamento

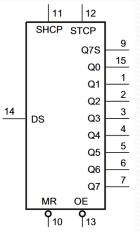

• Exemplo: 74595 – registrador de deslocamento de 8 bits

| Control  |            | Input | Output |    | Function |     |                                                                                                                                                                                                |  |  |

|----------|------------|-------|--------|----|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SHCP     | STCP       | OE    | MR     | DS | Q7S      | Qn  |                                                                                                                                                                                                |  |  |

| X        | Χ          | L     | L      | Χ  | L        | NC  | a LOW-level on MR only affects the shift registers                                                                                                                                             |  |  |

| X        | <b>↑</b>   | L     | L      | X  | L        | L   | empty shift register loaded into storage register                                                                                                                                              |  |  |

| X        | Χ          | Н     | L      | Χ  | L        | Z   | shift register clear; parallel outputs in high-impedance OFF-state                                                                                                                             |  |  |

| 1        | Х          | L     | Н      | Н  | Q6S      | NC  | logic HIGH-level shifted into shift register stage 0. Contents of all shift register stages shifted through, e.g. previous state of stage 6 (internal Q6S) appears on the serial output (Q7S). |  |  |

| X        | $\uparrow$ | L     | Н      | X  | NC       | QnS | contents of shift register stages (internal QnS) are transferred to the storage register and parallel output stages                                                                            |  |  |

| <b>↑</b> | <b>↑</b>   | L     | Н      | X  | Q6S      | QnS | contents of shift register shifted through; previous contents of the shift register is transferred to the storage register and the parallel output stages                                      |  |  |

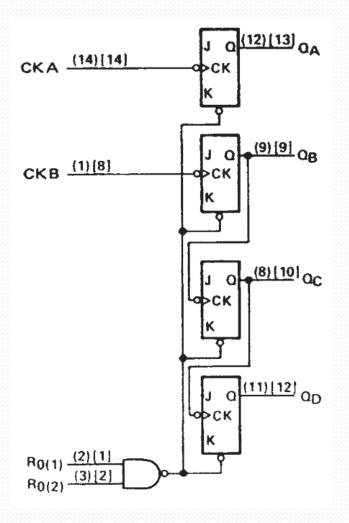

### Contadores

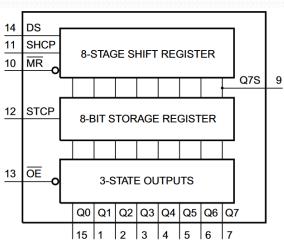

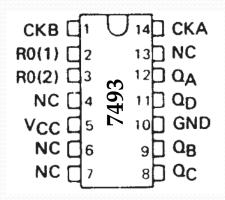

• Exemplo: 7493 – contador binário de 4 bits

| RESET                               | INPUTS | OUTPUT  |         |    |    |  |  |  |  |

|-------------------------------------|--------|---------|---------|----|----|--|--|--|--|

| R <sub>0(1)</sub> R <sub>0(2)</sub> |        | $a_{D}$ | $a_{c}$ | QB | QA |  |  |  |  |

| Н                                   | Н      | L       | L       | L  | L  |  |  |  |  |

| L                                   | Х      | COUNT   |         |    |    |  |  |  |  |

| ×                                   | L      | COUNT   |         |    |    |  |  |  |  |

| COUNT | OUTPUT |         |    |    |  |  |  |  |  |

|-------|--------|---------|----|----|--|--|--|--|--|

| COON  | αD     | $a_{C}$ | QΒ | QA |  |  |  |  |  |

| 0     | L      | L       | L  | L  |  |  |  |  |  |

| 1     | L      | L       | L  | н  |  |  |  |  |  |

| 2     | L      | L       | Н  | L  |  |  |  |  |  |

| 3     | L      | L       | Н  | Н  |  |  |  |  |  |

| 4     | L      | H       | L  | L  |  |  |  |  |  |

| 5     | L      | Н       | L  | Н  |  |  |  |  |  |

| 6     | L      | Н       | Н  | L  |  |  |  |  |  |

| 7     | L      | Н       | Н  | Н  |  |  |  |  |  |

| 8     | н      | L       | L  | L  |  |  |  |  |  |

| 9     | н      | L       | L  | Н  |  |  |  |  |  |

| 10    | Н      | L       | Н  | L  |  |  |  |  |  |

| 11    | н      | L       | Н  | Н  |  |  |  |  |  |

| 12    | н      | Н       | L  | L  |  |  |  |  |  |

| 13    | н      | Н       | L  | Н  |  |  |  |  |  |

| 14    | Н      | Н       | Н  | L  |  |  |  |  |  |

| 15    | н      | Н       | Н  | Н  |  |  |  |  |  |

- Estratégia de projeto:

- Inicialmente, preparamos um programa sequencial que descreve a tarefa de computação que desejamos implementar.

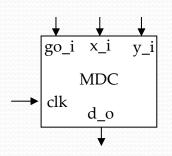

- Exemplo: Cálculo do máximo divisor comum

```

0: int x, y;

1: while (1) {

2:    while (!go_i);

3:    x = x_i;

4:    y = y_i;

5:    while (x != y) {

6:        if (x < y)

7:        y = y - x;

else

8:        x = x - y;

}

9:    d_o = x;

}</pre>

```

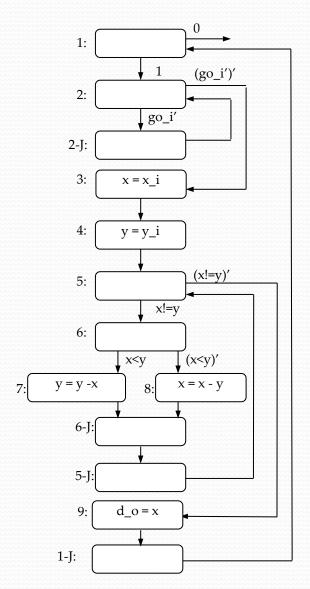

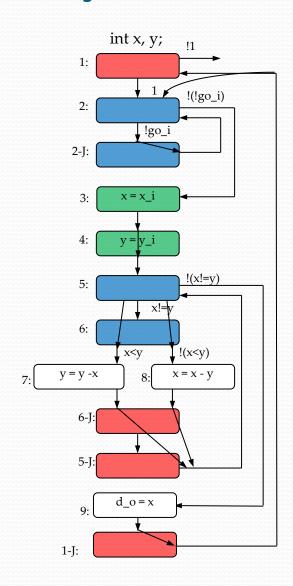

Convertemos o programa em um diagrama de estados, no qual os estados e os arcos podem incluir expressões aritméticas, e tais expressões podem utilizar entradas e saídas externas bem como variáveis.

- Este diagrama é chamado de **máquina de estados finitos com datapath (FSMD)**.

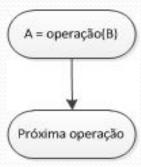

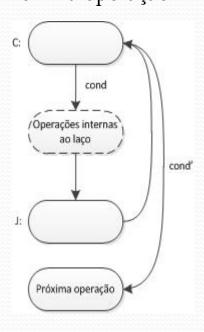

- Para isto, usamos alguns modelos básicos de conversão de comandos típicos de linguagens de programação em um diagrama de transição de estados.

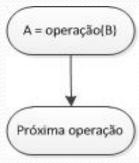

#### Atribuição de valor a uma variável

A = operação(B) Próxima operação

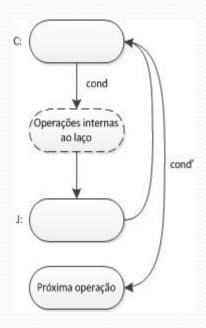

#### Laço de repetição

Enquanto (cond) {

Operações internas ao laço

}

Próxima operação

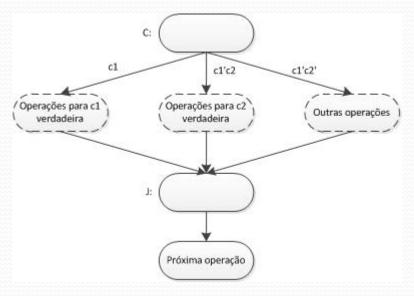

#### Desvio condicional

Se (c1)

Operações para c1 verdadeira Senão, se (c2)

Operações para c2 verdadeira Senão,

Outras operações Próxima operação

### Atribuição de valor a uma variável

```

0: int x, y;

1: while (1) {

2: while (!go_i);

3: x = x_i;

4: y = y_i;

5: while (x != y) {

6: if (x < y)

7: y = y - x;

else

8: x = x - y;

}

9: d_o = x;

```

#### Laço de repetição

#### Desvio condicional

```

0: int x, y;

1: while (1) {

2:    while (!go_i);

3:    x = x_i;

4:    y = y_i;

5:    while (x != y) {

6:        if (x < y)

7:        y = y - x;

else

8:        x = x - y;

}

9:    d_o = x;

}</pre>

```

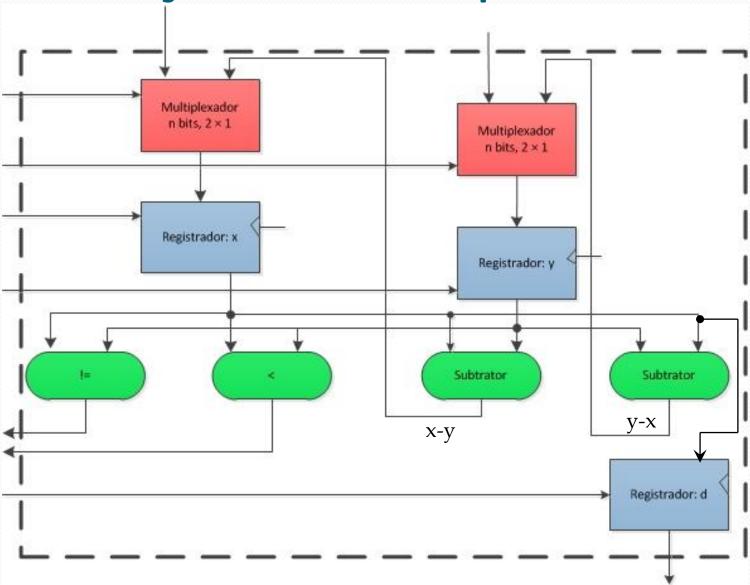

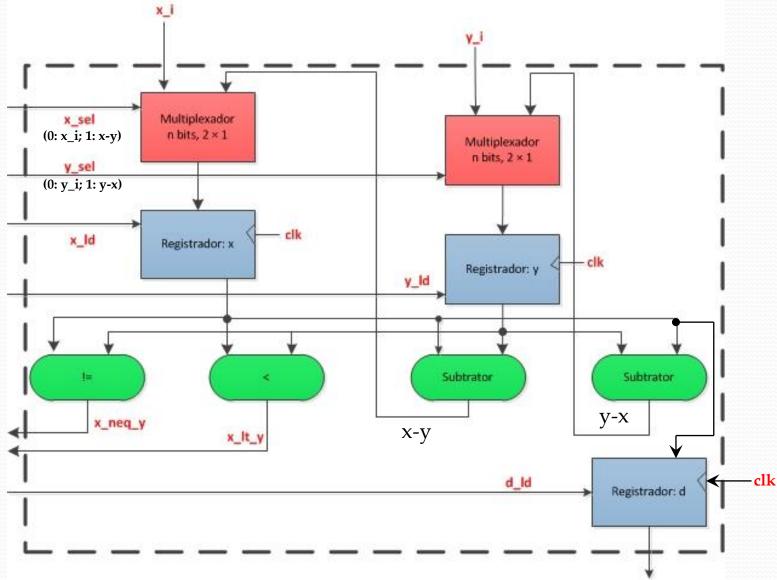

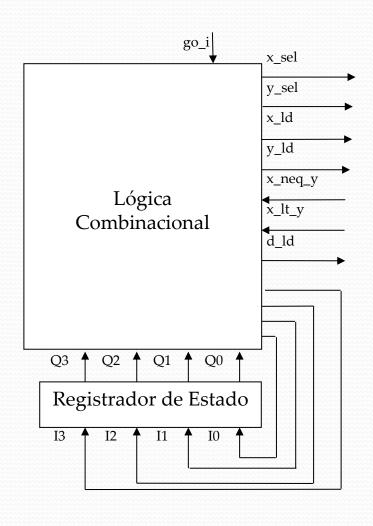

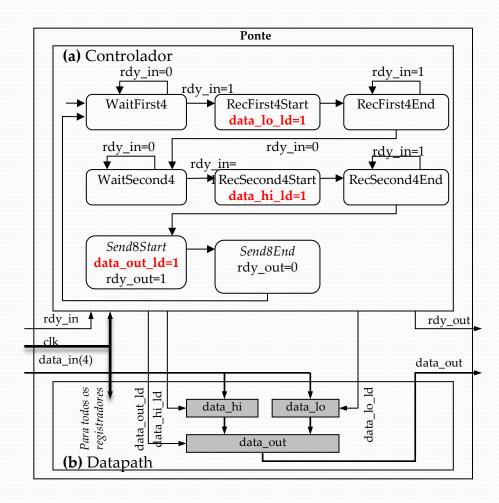

Dividimos a funcionalidade em uma parte referente ao datapath e outra referente ao controlador.

• Datapath: interconexão de componentes combinacionais (que realizam as operações do processador) e sequenciais (registradores para armazenamento temporário de dados).

• Controlador: é descrito por uma máquina de estados finitos (FSM) pura, i.e., que contém apenas ações e condições booleanas.

• O datapath pode ser construído da seguinte maneira:

1. Aloca-se um registrador para qualquer variável declarada.

Registrador: x

Registrador: y

```

0: int x, y;

1: while (1) {

2: while (!go_i);

3: x = x_i;

4: y = y_i;

5: while (x!= y) {

6: if (x < y)

7: y = y - x;

else

8: x = x - y;

}

9: d_o = x;

}

```

Registrador: d

• O datapath pode ser construído da seguinte maneira:

2. Aloca-se uma unidade funcional para cada operação lógico-aritmética na FSMD.

Registrador: x

Registrador: y

```

0: int x, y;

1: while (1) {

2: while (!go_i);

3: x = x_i;

4: y = y_i;

5: while (x != y) {

6: if (x < y)

7: y = y - x;

else

8: x = x - y;

}

9: d_o = x;

}

```

Subtrator

Subtrator

Registrador: d

• O datapath pode ser construído da seguinte maneira:

- 3. Conectam-se as portas lógicas, os registradores e as unidades funcionais.

- Uso de multiplexadores para operação com diversas entradas

• O datapath pode ser construído da seguinte maneira:

4. Cria-se um identificador único para cada sinal de controle dos componentes do datapath.

- De posse do datapath, podemos modificar a FSMD de modo a obter uma FSM que descreve o comportamento do controlador.

- A FSM possui os mesmos estados e transições da FSMD. Entretanto, as operações existentes são convertidas em versões booleanas, fazendo uso dos sinais de controle do datapath.

- Operações de escrita em variável:

- ➤ Ajustar os sinais de seleção de multiplexadores e sinais de carregamento (*load*) em registradores.

- Operações lógicas em uma condição:

- ➤ Usar os sinais de controle de saída da unidade funcional correspondente.

#### Cuidados:

As operações especificadas em um mesmo estado ocorrem em paralelo.

➤Operações de escrita em uma variável não atualizam seu valor imediatamente — é preciso esperar pelo próximo ciclo de relógio.

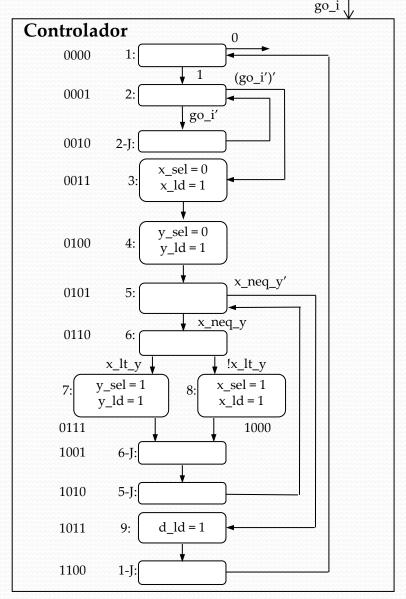

Modelo de implementação do controlador

- É possível completar o projeto do controlador implementando a FSM através da técnica de projeto de lógica sequencial descrita anteriormente.

- Nesta etapa, ferramentas computacionais de auxílio ao projeto (CAD) que automatizem o processo de desenvolvimento das lógicas combinacional e sequencial podem ser muito úteis. (Por exemplo, ferramentas de síntese).

| Inputs |    |    |    |         |        | Outputs |    |    |    |    |       |       |      |      |      |

|--------|----|----|----|---------|--------|---------|----|----|----|----|-------|-------|------|------|------|

| Q3     | Q2 | Q1 | Q0 | x_neq_y | x_lt_y | go_i    | I3 | I2 | I1 | IO | x_sel | y_sel | x_ld | y_ld | d_ld |

| 0      | 0  | 0  | 0  | *       | *      | *       | 0  | 0  | 0  | 1  | X     | Х     | 0    | 0    | 0    |

| 0      | 0  | 0  | 1  | *       | *      | 0       | 0  | 0  | 1  | 0  | X     | Х     | 0    | 0    | 0    |

| 0      | 0  | 0  | 1  | *       | *      | 1       | 0  | 0  | 1  | 1  | Х     | X     | 0    | 0    | 0    |

| 0      | 0  | 1  | 0  | *       | *      | *       | 0  | 0  | 0  | 1  | X     | X     | 0    | 0    | 0    |

| 0      | 0  | 1  | 1  | *       | *      | *       | 0  | 1  | 0  | 0  | 0     | Х     | 1    | 0    | 0    |

| 0      | 1  | 0  | 0  | *       | *      | *       | 0  | 1  | 0  | 1  | X     | 0     | 0    | 1    | 0    |

| 0      | 1  | 0  | 1  | 0       | *      | *       | 1  | 0  | 1  | 1  | X     | X     | 0    | 0    | 0    |

| 0      | 1  | 0  | 1  | 1       | *      | *       | 0  | 1  | 1  | 0  | X     | X     | 0    | 0    | 0    |

| 0      | 1  | 1  | 0  | *       | 0      | *       | 1  | 0  | 0  | 0  | X     | X     | 0    | 0    | 0    |

| 0      | 1  | 1  | 0  | *       | 1      | *       | 0  | 1  | 1  | 1  | X     | X     | 0    | 0    | 0    |

| 0      | 1  | 1  | 1  | *       | *      | *       | 1  | 0  | 0  | 1  | X     | 1     | 0    | 1    | 0    |

| 1      | 0  | 0  | 0  | *       | *      | *       | 1  | 0  | 0  | 1  | 1     | X     | 1    | 0    | 0    |

| 1      | 0  | 0  | 1  | *       | *      | *       | 1  | 0  | 1  | 0  | X     | Х     | 0    | 0    | 0    |

| 1      | 0  | 1  | 0  | *       | *      | *       | 0  | 1  | 0  | 1  | X     | Х     | 0    | 0    | 0    |

| 1      | 0  | 1  | 1  | *       | *      | *       | 1  | 1  | 0  | 0  | Х     | Х     | 0    | 0    | 1    |

| 1      | 1  | 0  | 0  | *       | *      | *       | 0  | 0  | 0  | 0  | X     | Х     | 0    | 0    | 0    |

| 1      | 1  | 0  | 1  | *       | *      | *       | 0  | 0  | 0  | 0  | X     | Х     | 0    | 0    | 0    |

| 1      | 1  | 1  | 0  | *       | *      | *       | 0  | 0  | 0  | 0  | X     | Х     | 0    | 0    | 0    |

| 1      | 1  | 1  | 1  | *       | *      | *       | 0  | 0  | 0  | 0  | X     | Х     | 0    | 0    | 0    |

## Projeto de Processadores Dedicados – Nível de Registradores

- Em alguns casos, é preferível iniciar o projeto diretamente com a elaboração de uma FSMD:

- ➤ Quando a temporização ou o comportamento ciclo a ciclo do sistema é crucial (e.g., circuitos de espera e/ou sincronização).

## Projeto de Processadores Dedicados – Nível de Registradores

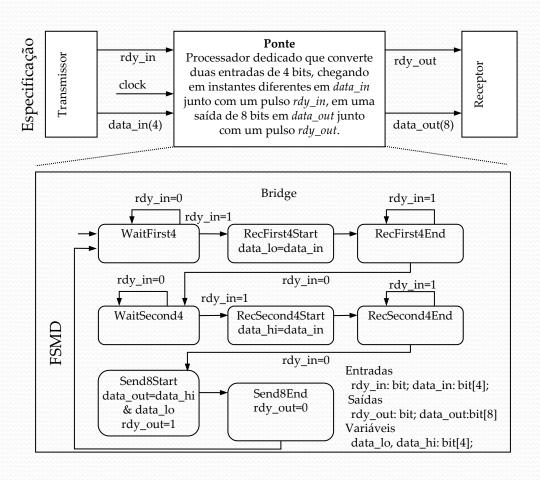

• Exemplo: Ponte entre um barramento de 4 bits e um barramento de 8 bits.

## Projeto de Processadores Dedicados – Nível de Registradores

• Exemplo: Ponte entre um barramento de 4 bits e um barramento de 8 bits.

### Otimização de Processadores Dedicados

- A estratégia de projeto de processadores dedicados vista anteriormente oferece uma maneira sistemática para construir o datapath e para obter a FSM que descreve o controlador.

- No entanto, muitas oportunidades para simplificar os componentes do processador foram desconsideradas.

#### Exemplo:

- > Estados que não executam operação alguma.

- > Repetição desnecessária de unidades funcionais.

#### Otimização de Processadores Dedicados

- Por que isso é importante?

- No contexto de sistemas embarcados, otimizar os componentes do processador pode ser crucial para atingir uma implementação que atenda adequadamente aos requisitos desejados quanto às métricas de projeto, como velocidade de processamento, consumo de potência e tamanho.

- ➤ Visa alcançar os melhores valores possíveis para as métricas de projeto.

#### Otimização do Programa

- Há várias partes associadas ao projeto de um processador dedicado em que surgem oportunidades para otimização:

- > Programa

- >FSMD

- **>** Datapath

- >FSM

### Otimização do Programa

Análise do algoritmo em termos de sua complexidade computacional no tempo e no espaço.

• Exemplo:

```

0: int x, y, r;

1: while (1) {

2: while (!go_i);

3: if (x_i \ge y_i) {

4: x=x i;

5: y=y_i;

6: else {

7: x=y_i;

y=x_i;

9: while (y != 0) {

10: r = x \% y;

11: x = y;

12:

y = r;

13: d \circ = x;

```

Fazendo uso de uma operação que computa de modo eficiente o resto de uma divisão, podemos reduzir o número de iterações em relação ao primeiro algoritmo.

### Otimização da FSMD

#### Possíveis melhorias:

- Fusão de estados

- ➤ Estados com constantes especificando as transições condicionais podem ser eliminados pois a transição destes estados é sempre a mesma.

- ➤ Estados adjacentes que realizam operações independentes podem ser reunidos em um único estado.

- Separação de estados

- Estados associados a operações complexas podem ser quebrados em estados menores para reduzir o tamanho do *hardware*.

#### Otimização da FSMD

*Eliminação do estado 1* – transições possuem valores constantes.

Fusão do estado 2 com o estado 2J – eliminação do loop entre eles pois não há operações no laço.

*Fusão dos estados 3 e 4* – as operações são independentes entre si.

*Fusão dos estados 5 e 6* – transições a partir do estado 6 podem ser realizadas no estado 5.

*Eliminação dos estados 5J e 6J* – as transições de cada estado podem ser realizadas a partir do estado 7 e 8, respectivamente.

*Eliminação do estado 1-J* – transições a partir do estado 1-J podem ser feitas diretamente a partir do estado 9.

Atenção: essas modificações alteram a temporização da FSMD!

### Otimização do Datapath

- Economia de unidades funcionais:

- ➤ Podemos compartilhar o uso de unidades funcionais no datapath, em vez de destinar uma para cada operação lógico-aritmética realizada (desde que tais operações ocorram em estados distintos).

- Além disso, existem diferentes componentes no nível de transferência entre registradores que podem compor um *datapath*: as peculiaridades de cada dispositivo podem ser benéficas ou não dependendo do contexto e das métricas de projeto para aquele sistema embarcado.

### Otimização da FSM

- Entram em cena questões envolvendo:

- A codificação dos estados, que exerce influência na complexidade do circuito combinacional que gera o próximo estado.

- A minimização do número de estados, através da fusão de estados equivalentes.

#### Resumo

- Processadores dedicados:

- ➤ Possuem hardware especialmente selecionado para realizar a tarefa desejada.

- > Técnica sistemática de projeto.

- ➤ Podem ser desenvolvidos a partir de um algoritmo (programa) ou de uma FSMD.

- ➤ Otimização em todos os níveis pode levar a implementações que satisfaçam os requisitos de projeto.