### Experimento IV – Transistores MOS e Estrutura CMOS

## 1 Objetivo

Levantar as curvas características de um transistor MOS e saber identificar através delas as três regiões de operação. Familiarizar-se com os principais prâmetros nominais fornecidos pelos fabricantes. Conhecer a estrutura CMOS e a sua aplicação na implementação de portas lógicas.

## 2 Estudo Dirigido

- 1. Desenhe esquematicamente a estrutura do transistor de efeito de campo de óxido de semicondutor (MOSFET) de canal n, indicando os três terminais (dreno, fonte e porta).

- 2. Existem MOSFETs de modo depleção e os de modo crescimento/intensificação. Qual é a diferença entre estes dois modos de operação? Qual é o estado "desligado" ( $turn\ off$ ) de cada modo em termos da tensão  $V_{GS}$ ?

- 3. Qual é a principal diferença entre a operação de um JFET e a de um MOSFET de modo depleção?

- 4. Por que é importante sempre ligar o substrato de um circuito integrado de MOSFETs de canal n no potencial mais baixo e de canal p no potencial mais alto?

- 5. Por que se recomenda a curto-circuitar os terminais fonte e dreno dos transistores não utilizados de um circuito integrado de FETs?

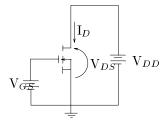

- 6. Dado o esquemático para levantamento das curvas características de um transistor MOS de modo crescimento:

Esboce a família de curvas de dreno de um transistor MOS ( $I_D \times V_{DS}$ ) parametrizado em  $V_{GS}$ , indicando a tensão de limiar ( $V_{GS(th)}$ ), a região de operação como fonte de corrente, a região ôhmica e a região de ruptura. Em qual região a corrente  $I_D$  praticamente independe da tensão  $V_{DS}$ ? E em qual região ela é uma função linear de  $V_{DS}$ ?

7. Na região de (corrente de) saturação a relação entre  $V_{GS}$  e  $I_D$  pode ser aproximada por

$$I_{DS} = k_p (V_{GS} - V_{GS(th)})^2,$$

onde  $k_p$  é conhecido como **parâmetro de condutividade**. Como se pode estimar o valor de  $k_p$  a partir da curva  $\sqrt{I_D} \times V_{GS}$ .

- 8. Como se pode traçar uma curva de transferência ( $I_D \times V_{GS}$ ) para uma específica tensão  $V_{DS}$  a partir de uma família de curvas de dreno de um transistor? Como se determina a partir da curva de transferência de um MOS a sua transcondutância  $g_m$  em torno de um ponto quiescente específico?

- 9. Dado um ponto quiescente de um transistor MOS, mostre que a relação entre a sua transcondutância  $g_m$  e o ganho de tensão  $G_v$  de pequenos sinais ca em torno deste ponto pode ser dada por

$$G_v = -g_m R_D$$

onde  $R_D$  é a resistência que deve ser inserido entre a fonte de alimentação  $\mathbf{V}_{DD}$  e o terminal de dreno do transistor.

- 10. Considerando  $g_m$ =0.003. Determine o valor da resistência que deve ser inserida entre uma fonte  $V_{DD}$  e o terminal de dreno de um MOS para que se obtenha  $G_v = 4$ .

- 11. Valem para os transistores MOS os problemas de ceifamento nos picos discutidos nos Experimentos 2 e 3?

- 12. O que você entende por MOS complementar (CMOS)?

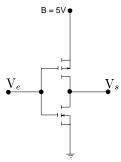

- 13. Desenhe o esquemático elétrico do seguinte circuito, com uso de um CI 4007.

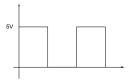

Explique o princípio de funcionamento do circuito para duas situações (a)  $V_e = 0V$  e (b)  $V_e = 5V$ . Desenhe a forma de onda de saída  $V_s$  quando se aplique no terminal de entrada  $V_e$  a seguinte onda:

Qual é a forma de onda da corrente em função do sinal de entrada  $V_e$ ? A partir das formas de onda, explique a seguinte afirmação comumente encontrada nos livros-texto: "A principal vantagem no uso de projetos CMOS é o seu consumo de potência extremamente baixo. Ele é um dispositivo que consome uma potência apreciável só quando muda de estado." (Observação: A potência de dissipação P depende da capacitância C de saída, da frequência de operação f e da tensão  $V_{DD} - P = CfV_{DD}^2$ .)

- 14. Qual é a relação entre a corrente que circula num capacitor e a variação da sua tensão num intervalo de tempo  $\Delta t$ ? Se ligarmos um capacitor de 1nF entre os terminais de saída e o terra do circuito do item 13, como as formas de onda de saída serão alteradas?

- 15. Projete, com uso de um componente ativo, CI 4007, e alguns componentes passivos R e C um circuito que produza o seguinte sinal em resposta à excitação com um sinal de entrada quadrado de frequência 5KHz:

Desenhe o esquema elétrico do circuito.

- 16. Consulte na folha de dados os valores dos principais parâmetros do CI 4007.

- 17. Leia atentamente as propostas do experimento e faça os esquemáticos elétricos das montagens.

#### 3 Implementação de Portas Lógicas com uso dos CMOS

Devido ao seu baixo consumo de energia, os transistores CMOS são amplamente utilizados na realização de portas lógicas utilizadas em circuitos digitais. As portas lógicas são elementos básicos de construção dos circuitos digitais. Eles operam um ou mais sinais lógicos de entrada, "0" e "1", para produzir uma e somente uma saída, a qual é dependente da função lógica implementada no circuito. Um computador é, por exemplo, constituído por uma infinidade de circuitos lógicos, que executam entre outras as seguintes funções básicas:

- 1. operações lógicas e aritméticas

- 2. sequenciamento dos sinais de controle

- 3. armazenamento de dados

Três operadores lógicos básicos são:

**NOT:** 1 = NOT(0); 0 = NOT(1);

**AND:** 1 = 1 AND 1; 0 = 1 AND 0; 0 = 0 AND 1; 0 = 0 AND 0;

**OR:** 1 = 1 OR 1; 1 = 1 OR 0; 1 = 0 OR 1; 0 = 0 OR 0.

Existem várias formas para implementar as portas lógicas. Na maioria dos sistemas digitais, utilizam-se as portas constituídas com a tecnologia CMOS. Neste caso, os níveis de tensão são utilizados para representar os sinais lógicos "0" e "1".

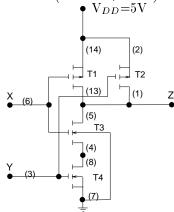

No item 13 apresentamos uma "porta inversora". Agora analisaremos a implementação de duas outras funções, começando com a porta lógica NAND (= NOT + AND)

Podemos construir a seguinte tabela-verdade ao analisarmos todas as possíveis combinações das entradas, considerando que os níveis de tensão 0 e 5 V correspondem aos sinais lógicos "0" e "1", respectivamente.

| X        | Y        | T1                      | T2                      | T3                      | T4                      | ${f Z}$  |

|----------|----------|-------------------------|-------------------------|-------------------------|-------------------------|----------|

| 0V ("0") | 0V ("0") | $\operatorname{Conduz}$ | $\operatorname{Conduz}$ | Não Conduz              | Não Conduz              | 5V ("1") |

| 0V ("0") | 5V ("1") | $\operatorname{Conduz}$ | Não Conduz              | Não Conduz              | $\operatorname{Conduz}$ | 5V ("1") |

| 5V ("1") | 0V ("0") | Não Conduz              | $\operatorname{Conduz}$ | $\operatorname{Conduz}$ | Não Conduz              | 5V ("1") |

| 5V ("1") | 5V ("1") | Não Conduz              | Não Conduz              | $\operatorname{Conduz}$ | $\operatorname{Conduz}$ | 0V ("0") |

|          |          |                         | MOD                     | 1 - 0 - 0               |                         |          |

Como seria a implementao de uma porta NOR com uso de 5 CIs?

| ĺ | X        | Y        | T1                      | T2                      | Т3                      | T4         | Z        |

|---|----------|----------|-------------------------|-------------------------|-------------------------|------------|----------|

| ſ | 0V ("0") | 0V ("0") | $\operatorname{Conduz}$ | $\operatorname{Conduz}$ | Não Conduz              | Não Conduz | 5V ("1") |

| ſ | 0V ("0") | 5V ("1") | $\operatorname{Conduz}$ | Não Conduz              | Não Conduz              | Conduz     | 0V ("0") |

| ſ | 5V ("1") | 0V ("0") | Não Conduz              | $\operatorname{Conduz}$ | $\operatorname{Conduz}$ | Não Conduz | 0V ("0") |

|   | 5V ("1") | 5V ("1") | Não Conduz              | Não Conduz              | $\operatorname{Conduz}$ | Conduz     | 0V ("0") |

Tente ainda implementar com uso de um CI 4007 uma porta AND e uma porta OR.

# 4 Componentes

- 2 CIs 4007

- ullet 2 soquetes de 7 pinos

- 1 resistor de 100  $\Omega$ .

- 1 resistor a ser determinado.

- (Opcional) 1 resistor de 10 k $\Omega$ .

Trazer ainda uma folha de papel milimetrado.

## 5 Parte Experimental

Importante: Na montagem, curto-circuitar os terminais de dreno e fonte de todos os transistores não utilizados. O substrato do canal p e o do canal n devem estar no potencial mais alto e mais baixo, respectivamente.

Características de um MOS: Utilize o circuito mostrado no item 6 da seção 2 para obter algumas características do transistor CI 4007

1. Complete a seguinte tabela:

|              | $I_D(mA)$   |             |             |             |             |  |

|--------------|-------------|-------------|-------------|-------------|-------------|--|

| $V_{DS}$ (V) | $V_{GS}=2V$ | $V_{GS}=3V$ | $V_{GS}=4V$ | $V_{GS}=5V$ | $V_{GS}=6V$ |  |

| 0.1          |             |             |             |             |             |  |

| 0.25         |             |             |             |             |             |  |

| 0.5          |             |             |             |             |             |  |

| 1.0          |             |             |             |             |             |  |

| 2.0          |             |             |             |             |             |  |

| 4.0          |             |             |             |             |             |  |

| 6.0          |             |             |             |             |             |  |

| 8.0          |             |             |             |             |             |  |

- 2. Componha numa folha de papel milimetrado uma família de curvas de dreno, parametrizadas em

- 3. Trace a curva de transcondutância  $I_D \times V_{GS}$  para  $V_{DS}$ =4V. Determine graficamente a transcondutância  $(g_m)$  do transistor para  $V_{GS} = 4V$ . Indique os pontos da curva que você utilizou.

$$g_m = \frac{\Delta I_D}{\Delta V_{GS}} =$$

$\boxed{g_m = \frac{\Delta I_D}{\Delta V_{GS}} =}$ 4. Trace a curva  $\sqrt{I_D} \times V_{GS}$  para  $V_{DS} = 4V$ . Determine graficamente o parâmetro de condutividade  $k_p$  e a tensão de limiar  $\mathbf{V}_{GS(th)}$ .

Amplificador: Monte um amplificador de tensão de ganho G<sub>v</sub>=4 com o uso do CI 4007.

1. Verifique o funcionamento do circuito aplicando uma onda triangular de amplitude  $500 \mathrm{mV}_{pp}$ ,  $V_{offset}$ =4V e frequência 10KHz. Alimente ainda o circuito com  $V_{DD}$  = 8V. Compare o ganho obtido experimentalmente com o valor esperado. Inclua as formas de onda de entrada e de saída, com base nas quais você determinou o ganho  $G_v$ .

$$R_D =$$

$$G_v =$$

2. Varie a frequência do sinal de entrada para determinar experimentalmente a largura de banda do amplificador. Comente os resultados.

$$\begin{array}{c} \mathbf{f}_{c_i} = \\ \\ \mathbf{f}_{c_s} = \\ \\ \mathbf{Largura\ de\ banda} = \mathbf{f}_{c_s} - \mathbf{f}_{c_i} = \\ \end{array}$$

Desafio: A largura de banda é dependente do ganho do circuito? Justifique.

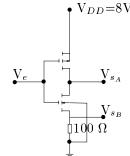

Características de um CMOS: Monte o circuito inversor CMOS como mostrado no esquemático:

1. Aplique como o sinal de entrada  $V_e$  uma onda senoidal de  $8V_{pp}$ ,  $V_{offset} = +4V$  e frequência=100Hz. Observe e imprima a forma de onda  $V_{s_A} \times V_e$ . Para isso, utilize o modo de operação XY do osciloscópio (DISPLAY > Format XY). Observe e imprima também a forma de onda  $V_{s_R} \times V_e$ . Comente os resultados obtidos.

- 2. Aplique como o sinal de entrada  $V_e$  uma onda quadrada de  $8V_{pp}$ ,  $V_{offset}$ =+4V e frequência=50kHz. Observe e imprima a forma de onda  $V_{s_A}$  × t. Observe e imprima também a forma de onda  $V_{s_B}$  × t. Comente os resultados obtidos.

- 3. Monte o circuito do item 15 da seção 2. Imprima as formas de onda de entrada e de saída para certificar o funcionamento do circuito.

Porta Lógica AND/OR: Monte o circuito NAND ou NOR da seção 3. Para verificar o funcionamento do circuito, aplique no terminal X uma onda quadrada (8  $V_{pp}$ ,  $V_{offset}$ =4V, frequência=100Hz) e no terminal Y um sinal constante ((1) terra e (2)  $V_{DD}$ ). Imprima para cada caso o sinal X, o sinal de saída Z e o sinal  $\overline{Z}$ . Comente os resultados.